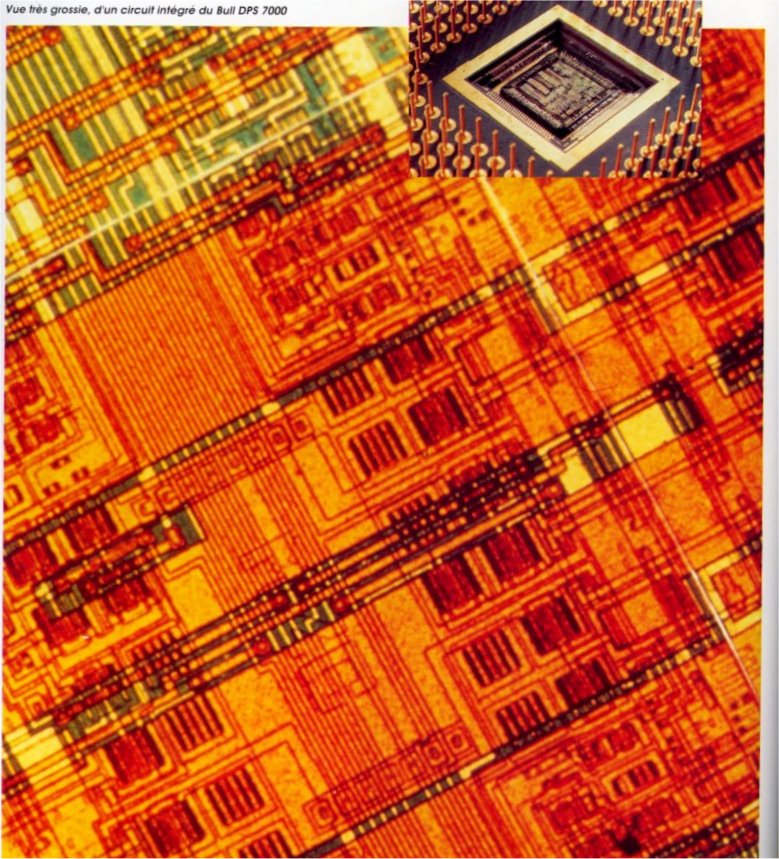

reproduction extraite du livre "Naissance d'un ordinateur" publiť par Bull 1992

TECHNOLOGIE |

TECHNOLOGY |

|

| L'unitť centrale du systŤme ARES est entiŤrement

rťalisťe en technologie VLSI CMOS, une des premiŤres rťalisations de

"mainframes" dans la technologie portťe par le dťveloppement des

micro-processeurs, encore de performances infťrieures ŗ celles de leurs aÓnťs

au milieu

des annťes 1980. Les circuits conÁus par Bull pour Ares ont ťtť rťalisťs sur une largeur de circuits de 2 Ķm de largeur, ce qui conduit sur une puce de 1 cm≤ ŗ environ 65000 transistors (en logique non entiŤrement rťpťtitive). Ces circuits sont interconnectťs par l'intermťdiaires de connecteurs ŗ 224 bornes dont 168 peuvent Ítre utilisťs pour la logique, les autres ťtant utilisťs pour les masses et l'alimentation. |

reproduction extraite du livre "Naissance d'un

ordinateur" publiť par Bull 1992

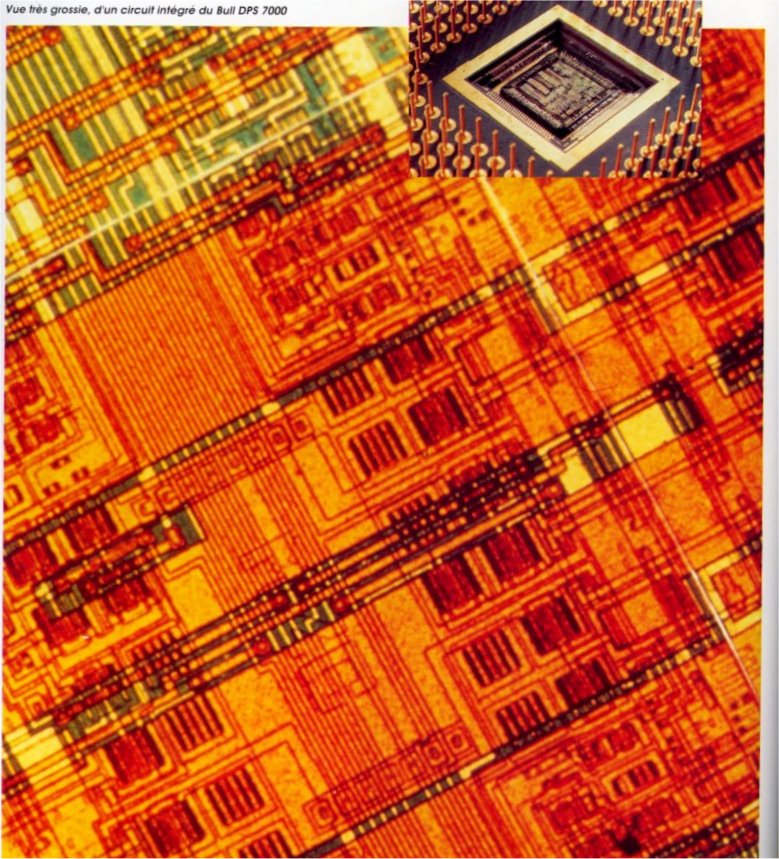

VLSI CMOS ARES , technologie 2 micron monté sur son

ruban de test.

1er plan : connecteur pour VLSI CMOS ARES, monté sur

Pin Grid Array (PGA).

2ème Plan : VLSI CMOS ARES monté sur PGA avec radiateur de refroidissement

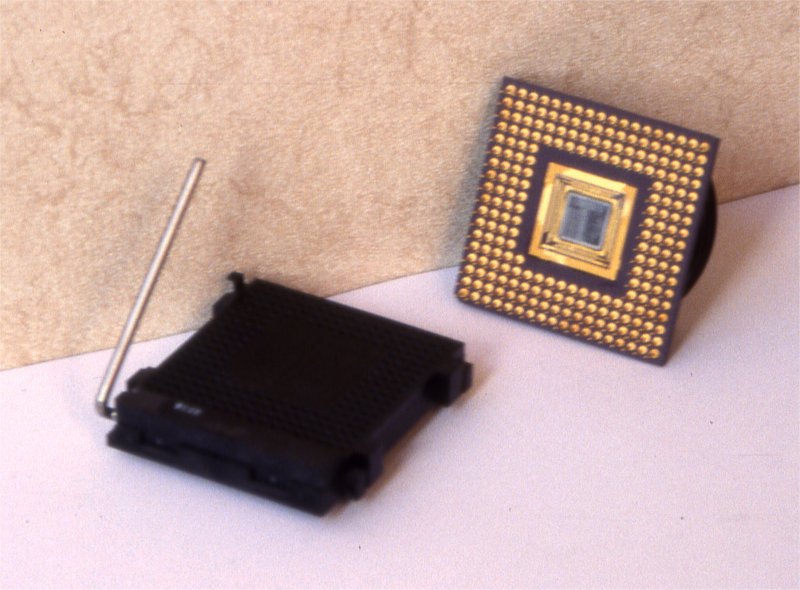

photographie d'une plaque processeur Ares

avec au premier plan sa carte fille contenant la mťmoire de contrŰle. Au

second plan les radiateurs des VLSI custom dťveloppťs par Bull.

photo © Jean Bellec 2004 d'aprŤs une plaque ldonnée à FEB par Dan Humblot.

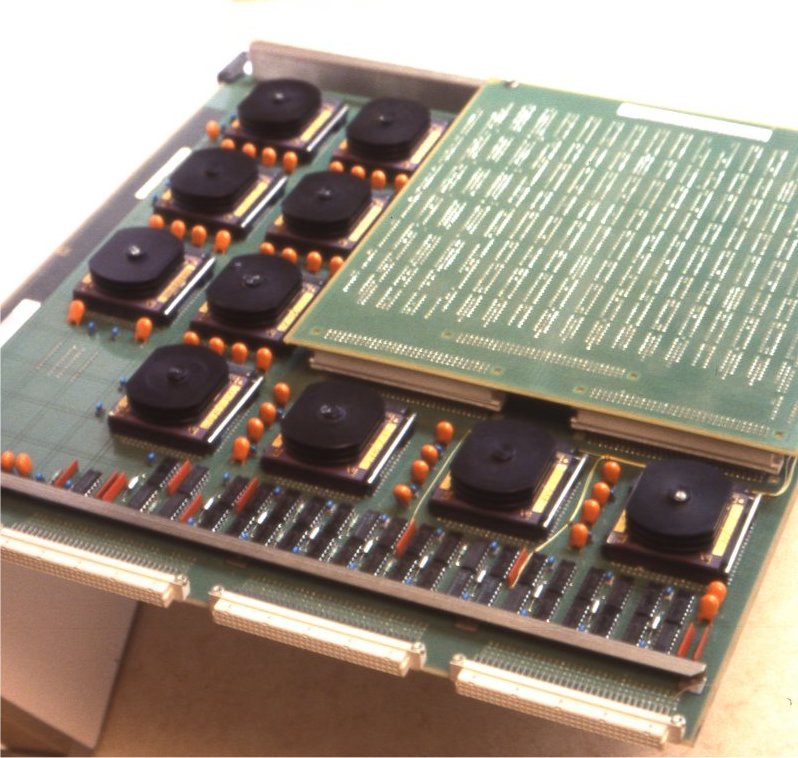

Perspective de la carte unité centrale du système

ARES montrant les connecteurs de raccordement au bus système.

Macropackaging

|

|

|

|

|

|

photos ©2007 FEB d'un DPS-7000 conservť ŗ Angers