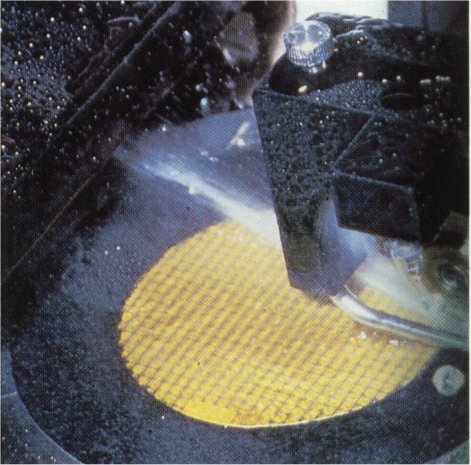

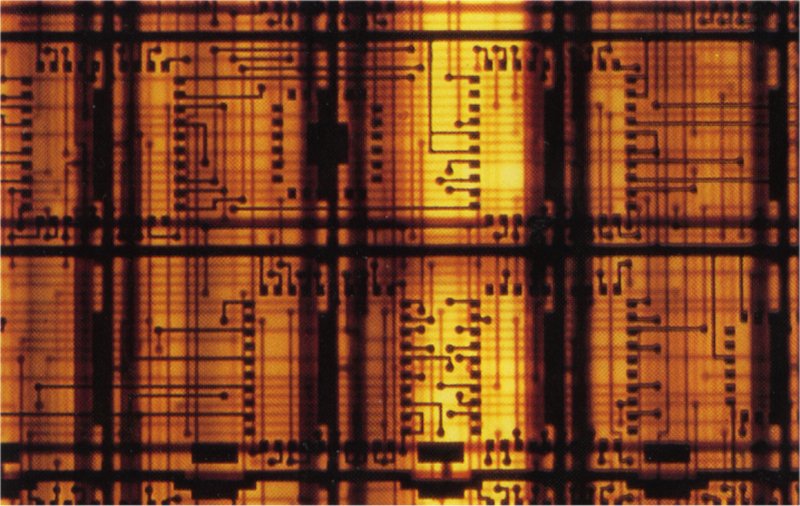

fig1- photo d'un wafer en cours de découpe

TECHNOLOGIE |

TECHNOLOGY |

|

| HISTOIRE Au cours des années 1970, si la technologie TTL avait fait ses preuves pour la technologie des ordinateurs moyens et petits, les constructeurs ne songeaient ŕ des structures d'architecture complexes (pipe-lines, caches) que pour des supercalculateurs. Un certain consensus se fit pour l'utilisation de la technologie ECL pour les grands ordinateurs classiques. Les fabricants de semi-conducteurs Texas et Motorola annoncčrent leurs séries TECL et MECL, tandis que IBM l'adoptait pour la plus partie haute de sa ligne. L'adoption d'une technologie de commutation rapide (moins de 10 ns) ne suffisait pas cependant ŕ équiper des ordinateurs performants, car une grande partie des délais étaient causés par la longueur et les caractéristiques d'impédance/capacité causés par les liaisons entre circuits. Si les constructeurs pouvaient compter sur une production de circuits par des tiers, il n'en était pas de męme de la conception du packaging qui restait spécifique des ordinateurs. C'est ainsi que les études de technologie de Bull (BGE puis Honeywell-Bull) s'orientčrent avec les départements de recherche de GE (puis de Honeywell) sur l'étude des différents niveaux de "packaging". A partir d'une étude préliminaire de General Electric, Bull développa la technologie TC32 pour les ordinateurs DPS-7 (Leo, Taurus, Lyra) livrés de 1981 ŕ 1987. Les circuits logiques CML (a variant of ECL) conçus par le département Études de Bull étaient fabriqués par un fondeur, essentiellement Atmel, héritier du département semi-conducteurs de GE et Honeywell. Ils étaient vendus ŕ Bull sous la forme de galettes (wafers) composés de circuits identiques. (fig 1) Bull Angers réalisait les opérations de sciage et de mise sur bandes en vue de la pose sur substrats par des machines automatiques. Les substrats multi-couches étaient entičrement construits par Bull de maničre analogue ŕ la fabrication des circuits imprimés (tels que celui du panneau arričre), mais avec des contraintes de finesse de tracé plus rigoureuses. Les conducteurs des substrats étaient des fils d'or déposés sur le substrat de céramique. Un essai d'utilisation du cuivre , ŕ des fins de réduction de coűt, fut un échec coűteux ŕ cause de phénomčnes d'électromigration rencontrés aussi par d'autres constructeurs. Aprčs soudure des circuits sur les substrats, il ne restait plus qu'ŕ assembler les substrats sur le circuit imprimé du panneau arričre ŕ l'aide de connecteurs classiques. BIBLIOGRAPHIE

|

HISTORY During the 1970s, while the TTL technology was completely proven for small and medium computers, manufacturers were using complex processor structures (e.g. pipe-lines, caches) only for supercomputers. They adopted ECL technology for large classic computers. Semiconductor manufacturers (such as TI and Motorola) were announcing TECL and MECL and IBM adopted ECL for their upper range. Using a fast (less than 10 ns) switching technology was not sufficient for fats computers because signals delay was largely due to the length and the characteristics of the links between logical circuits. The circuits themselves would be produced by independent vendors -the silicon founders-, but there was no independent vendor at that time to produce the overall packaging. The engineering department of Bull (Bul-GE then Honeywell-Bull) started studying the different levels of packaging, in collaboration with semi-conductors research departments of GE (later Honeywell). Based on a preliminary study of General Electric, Bull developed TC32 technology for its DPS-7 computers (Leo, Taurus, Lyra) sold from 1981 to 1987.

|

fig1- photo d'un wafer en cours de découpe

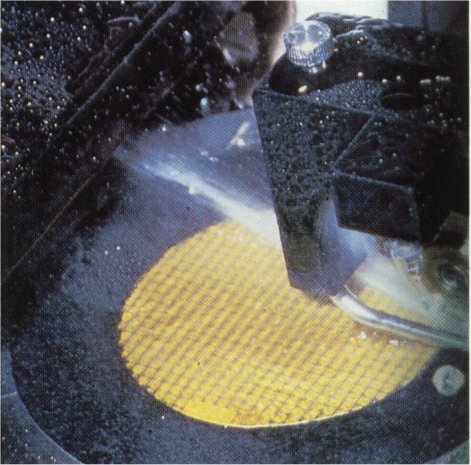

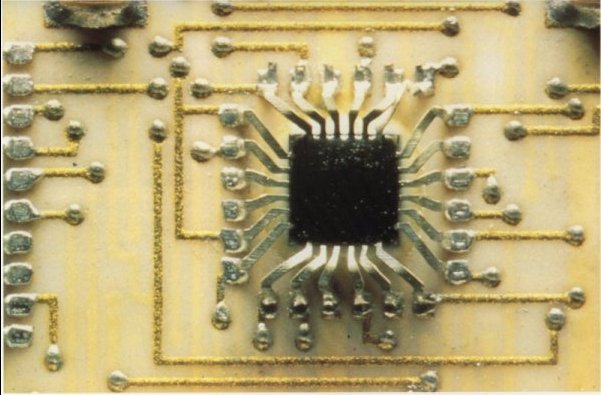

fig 2- photo d'un ruban TAB en cours de tests

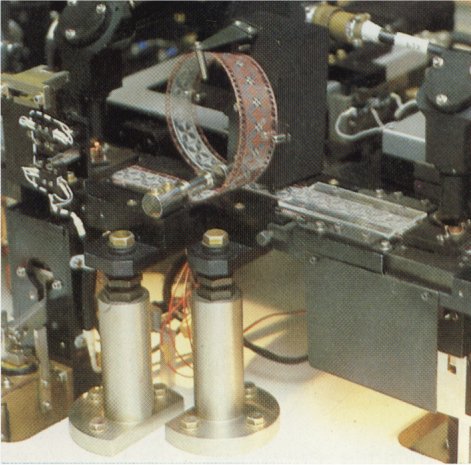

fig 3 -photo d'une puce CML aprčs séparation du ruban TAB et avant assemblage sur

le substrat

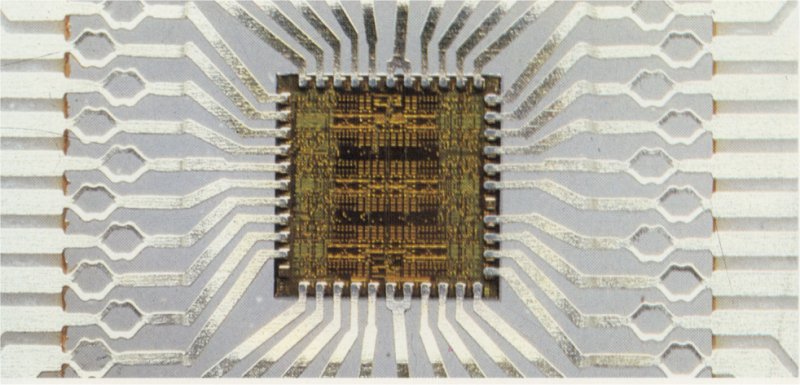

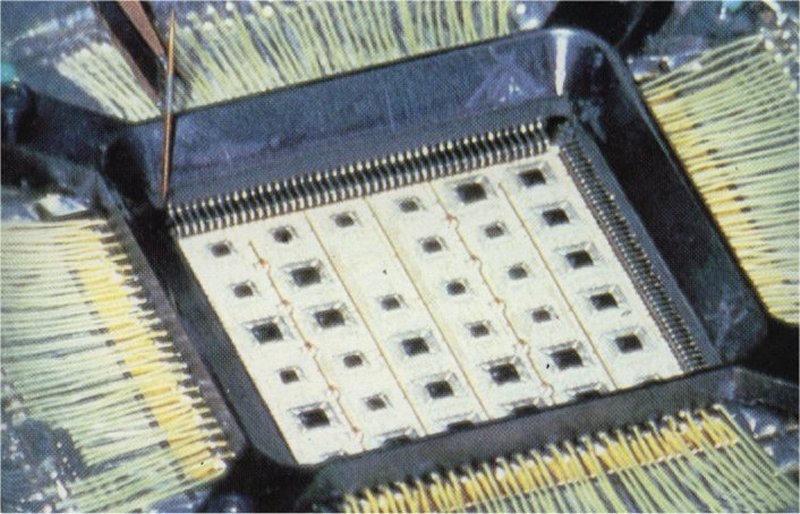

fig 4- photo d'un substrat multi-couches

fig 5- photo d'une puce CML aprčs assemblage sur la couche externe du substrat

fig 6- photo d'un substrat assemblé en cours de tests

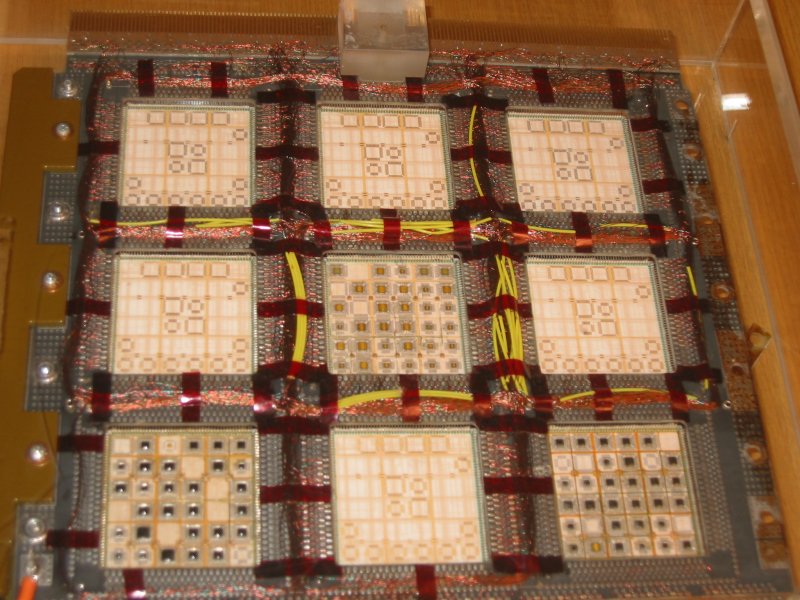

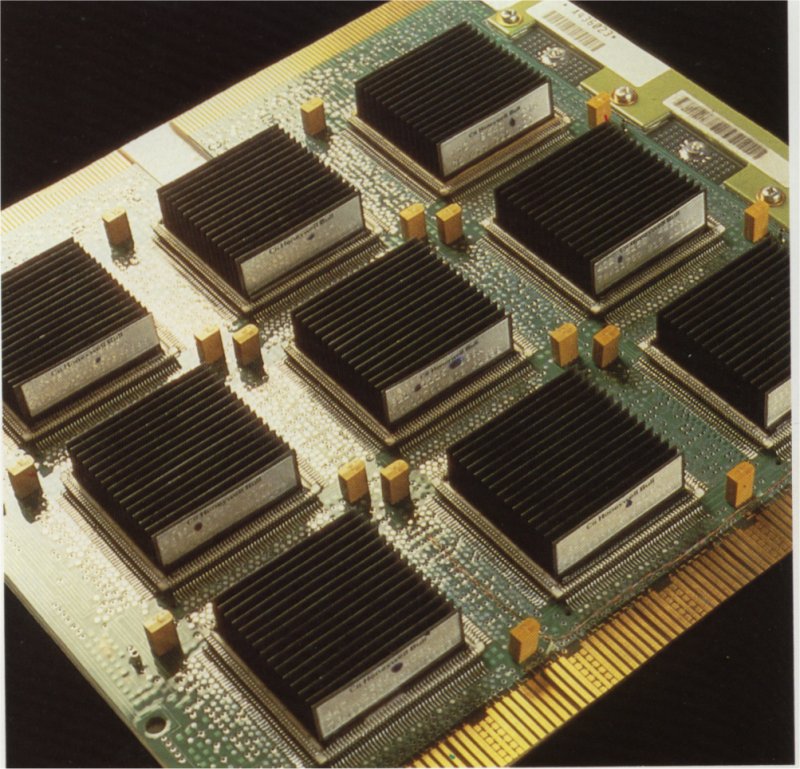

fig7. carte aprčs montage des substrats

(photo ©2004 Jean Bellec in FEB)

fig 8- photo d'une plaque assemblée avec ses radiateurs au dessus des substrats

©Bull photos ci-dessus sauf mention contraire d'aprčs notice Établissement d'Angers sept 1985