en construction

| Le projet

Auriga, est la dernière version de l'architecture matériel

DPS-7. Son objectif était de fournir une machine plus puissante que

les premiers DPS-7000 (Ares) dans des conditions de coût comparable

(c'est à dire sous la forme d'un processeur sur une plaque) en

utilisant la technologie CMOS avec une lithographie de 1.6 µm.

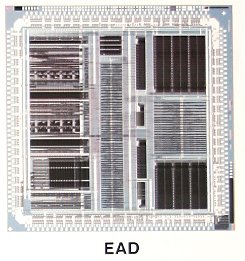

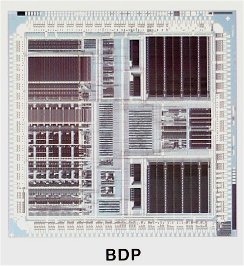

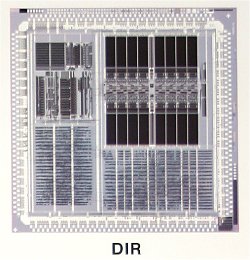

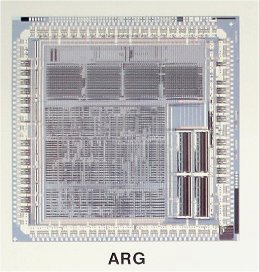

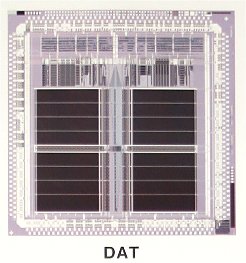

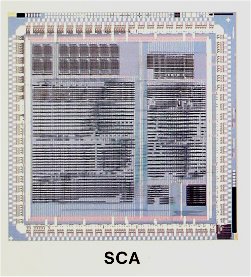

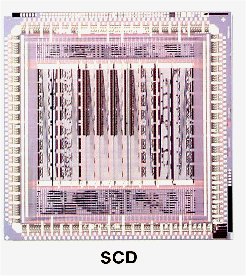

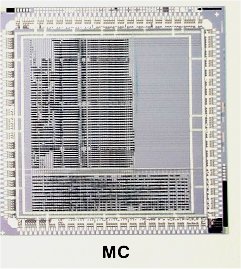

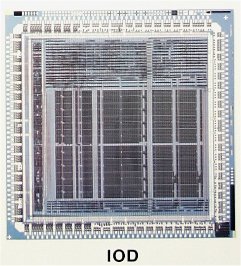

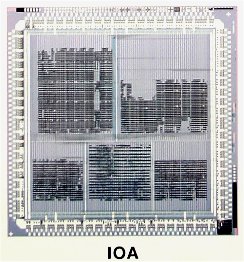

Le processeur proprement dit comporte 5 millions de transistors répartis en 6 circuits de 12 x12 mm avec 316 points de connexion. Cinq autres circuits ont été conçus pour le contrôleur de mémoire et le rattachement des entrées sorties. Il peut être partitionné en deux systèmes GCOS7. La structure

générale de l'unité centrale était dérivée de celle d'Ares, le bus

UMI étant relégué au niveau des entrées sorties et une nouvelle

interconnexion des processeurs était faite autour d'un nouveau bus

ASB (Auriga System Bus) à 500 Mo/s et d'un System Controller. La mémoire est constituée de chips DRAM 4Mbits et possède jusqu'à 8 modules de 64M octets. Le processeur comportait un pipe-line permettant un large recouvrement du temps des instructions. Le temps apparent de l'instruction AG4 était réduit à un seul cycle de 32ns. Le processeur comportait trois chemins de données, deux de 32 bits et un de 64 bits (utilisé entre autres pour accélérer les opérations en virgule flottante). L'exécution des microprogrammes étaient décentralisés dans les unités de traitement. Le chef de projet du programme était Michel Sakarovitch. Les architectes en étaient Michel Guillemet, Philippe Vallet et Jean-Jacques Pairault.. Le système de nom de code Vega est un système étroitement dérivé de Auriga, dont les entrées sorties utilisent des contrôleurs basés sur Multibus2 comme sur Ares phase 3.

|

The Auriga project was the last genuine

architecture of DPS-7 product line. Its objective was to deliver a

more powerful system than the first DPS-7000 (Ares) with similar

cost efficiency (one processor per board), using a 1.6 µm CMOS

technology. The processor itself includes 5 millions transistors on 6 chips (dimensions 12x12 mm, 316 pins). It is complemented by 5 other custom chips for the memory controller and the I/O trunks. The hardware system may contain up to 6 processors and 2 I/O units . Main memory use 4M bits DRAM chips and has up to 8 modules of 64 M bytes. The hardware configuration may be partitioned in 2 separate GCOS7 software systems.

|

|

|

|

|

|

|

|

|

|

|

|

photo ©2007 FEB cabinet principal du

système Auriga conservé à la FEB Angers