Matériel: les Sous-systèmes Périphériques

Par Jean

Bellec.

Les sous-systèmes périphériques constituaient une part très importante (plus de la moitié de la valeur) des systèmes des années 1970-1980, par leur prix (et leur coût), par leur encombrement et par la nécessité d'en optimiser le fonctionnement.

Les systèmes périphériques du Level

64 constituent pour la plupart une nouvelle génération développée par le groupe

Honeywell pour ses nouveaux systèmes (dont le Level 62 en Italie et le Level 66

aux États-Unis. La quasi totalité des appareils étaient construits ou du moins

assemblés au sein du groupe, à l'exception du téléimprimeur de la console qui

était lui fabriqué par … General Electric.

Progressivement,

il devint nécessaire de recourir à des fournitures externes OEM afin d'offrir

une offre compétitive avec le leader de l'industrie, ce qui était surtout criant

dans le domaine des disques magnétiques. Cependant la fusion avec CII permit en

1977-1982 de bénéficier des investissements faits par CII dans le domaine des

bandes magnétiques, domaine dont l'importance diminuait rapidement. L'émergence

d'une demande considérable et de l'offre correspondante dans le domaine des

micro-ordinateurs conduisit le Groupe Bull à renoncer au développement de

périphériques propres au début des années 1990 et progressivement à celui de

sous-systèmes non standards.

Architecture.

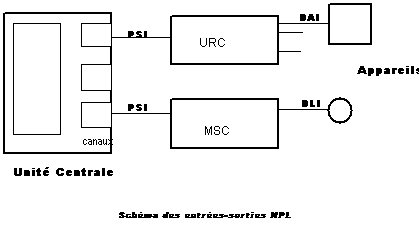

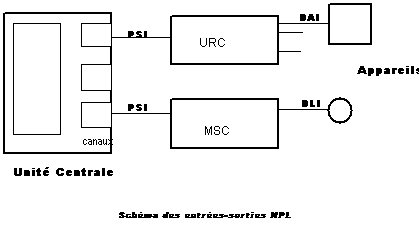

L'architecture de la nouvelle ligne se basait sur une série d'interfaces standard reprenant en gros les fonctionnalités définies pour l'IBM 360 pour l' interface canal (nommée PSI pour Peripheral System Interface) et des interfaces appareils l'une pour les périphériques fonctionnant avec une mémoire tampon de faible capacité (interface DLI pour Device Link Interface pour disques et bandes magnétiques) et une autre pour les appareils "unit records" ou de faible débit (interface DAI comme Device Adapter Interface). Ces interfaces d'appareils correspondaient à la frontière des responsabilités de développement, l'adaptation de l'appareil au DAI ou au DLI étant de la responsabilité du développeur de périphériques. Ces interfaces étaient considérées comme la propriété de Honeywell, la compagnie redoutant alors que des compagnies tierces ne capturent le marché des sous-systèmes.

Ces interfaces étaient matérialisées par des câbles qui fournissaient des liaisons étoilées, considérées comme plus sûres et plus fiables que des liaisons du type bus multipoints telles que les offraient IBM ou les premiers fabricants de mini-ordinateurs. La largeur des chemins de données sur l'interface PSI était de 8 bits (à noter que l'une extension éventuelle à 16-bits ne fut pas réalisée au sein du groupe Honeywell)

L'interface PSI faisait la liaison entre l'unité centrale (processeur et mémoire) et les contrôleurs de périphériques. Ceux-ci (appelés Peripherals Control Processors PCP) étaient au début de véritables mini-ordinateurs spécialisés réalisant les fonctions particulières de l'appareil, en les adaptant à la visibilité standard du logiciel. La programmation des opérations depuis GCOS se faisait au moyen d'un programme canal de longueur variable et composés d'instructions (CCE channel control entries). Il était possible de synchroniser les exécutions des programmes sur les canaux et les threads de l'unité centrale en fin ET en cours d'exécution des "channel programs". L'enchaînement de commandes (command chaining) était accompagnée d'enchaînements de transferts de données à des adresses non séquentielles (data chaining) et le "décor" des entrées-sorties comprenait en outre des instructions de branchement conditionnel permettant de planifier des boucles ou même des programmes de canaux perpétuellement actifs. Le "channel program" était interprété dans la partie IOC de l'unité centrale et transférait au processeur de périphériques uniquement les commandes et les données à transférer. Ce processeur contrôleur de périphériques (PCP) n'avait pas accès aux adresses de la mémoire centrale, ce qui n'exposait pas l'intégrité du système à la majorité des défaillances du matériel. Le désir de ne pas construire des édifices logiques dédiés à un modèle particulier de périphérique conduisait à faire du PCP un mini-ordinateur.

Cette architecture sera conservée jusqu'à la fin des années 1990 par une "émulation" des interfaces PSI sur différentes structures de matériels, de manière à conserver l'unicité du logiciel GCOS7 sur des plates-formes différentes.

Le premier système de la ligne de produits (de nom de code P7) avait son processeur conçu à Paris, cependant que les processeurs de périphériques magnétiques le MSC (Mass Storage Controller) ausi appelé et MTC (Magnetic Tape Controller) étaient conçus à Boston. Cette allocation était conforme à la répartition de la responsabilité des périphériques si bien que l'URC (Unit Record Controller) se voyait ainsi allouée à Paris, plus à même de coordonner les travaux de Belfort et certains développements italiens.

Ces contrôleurs étaient réalisés par des circuits d'intégration moyenne (MSI) en technologie TTL 74N. Le processeur de périphérique de base représentait un volume de un tiroir. Pour un système de bas de gamme, l'ensemble des contrôleurs représentaient environ le coût de l'unité centrale, ce qui conduisit à en limiter le nombre et à multiplexer sur chacun d'entre eux un grand nombre d'appareils (jusqu'à 16).

Les MSC et MTC avaient des

contraintes particulières dus au débit de transfert de données depuis ou vers

des appareils. Ces débits et les volumes de données transférées nécessitaient un

chemin direct depuis les DLI vers le PSI et le PCP avait plutôt un rôle

d'initialisation et de surveillance des transferts. Cette contrainte

architecturale justifiait autant que la proximité des fabricants d'appareils la

conception séparée de ces PCP. On notera aussi que, pour la ligne 66 (ligne

basée sur des mots de 36 bits), un autre type de PCP fut développé à

Phoenix.

Des contraintes particulières étaient placées sur ces

contrôleurs: outre les nouveaux périphériques qui étaient des appareils

compatibles avec IBM, ils devaient supporter en mode natif et en mode émulation

les appareils développés respectivement par Honeywell pour la série H-200

(caractères à 6 bits et données limitées par des drapeaux) et par General

Electric Italia pour la série GE-100. La reconnection des appareils en parc chez

les clients ainsi que l'émulation des programmes permettait une transition

rapide du parc vers le Level 64.

On pourrait passer sous silence l'utilisation du mini-ordinateur Honeywell 316 comme frontal de communications sous le nom de Datanet 2000. Ce matériel était une reconnection d'un matériel déjà existant sur le haut de gamme de la série H-3200.

L'URC, en grande partie parce qu'elle était développée auprès des responsables du système était la bonne à tout faire des contrôleurs de périphériques. A sa fonction de commande des "unit records" (appareil hérités de la mécanographie" s'ajoutèrent le support de nouveaux appareils et la fonction de processeur de service du système entier.

le tableau suivant reflète la diversité des appareils unit record connectés à l'URC

| appareil | nature | Lieu de

conception |

Lieu de

fabrication |

conception de l'électronique des appareils |

| CR1000 |

Lecteur de

cartes |

Boston | Belfort | Belfort/Paris |

| CR500 |

Lecteur de

cartes |

Boston |

Belfort |

Belfort/Paris |

| CP |

Perfo

cartes |

Boston | Belfort | Belfort |

| PR71 |

Imprimante à

bande |

Belfort | Belfort | Belfort/Paris |

| H112 |

Imprimante | Boston | Boston | Boston |

| I-51 | Imprimante

CMC7 |

Belfort | Belfort | Belfort |

| PT

R/P |

Lecteur/perfo

bandes |

Belfort | ||

| LD1 |

Lecteur

documents |

Belfort | Belfort | Belfort |

| TN300 |

Console |

General

Electric |

Paris | |

| CRT

console |

Console

écran |

Boston | Billerica | |

| Tape

cassette |

Pregnana |

Caluso |

Pregnana |

L'URC était de fait structuré comme

un mini-ordinateur 16-bits avec son propre système d'exploitation temps réel

MIOS, pilotant les drivers et au dessus duquel était placé un interpréteur de

décor 32-bits dans lequel s'exécutait le moniteur de tests.

Les drivers (appelés attachements) gèrent l'interprétation

des programmes canaux architecturés en micro-processes synchronisés par le MIOS. Deux de ses

attachements étaient consacrés aux fonctions de service du système, surveillant

deux interfaces spécialisées, l'une le connectant au processeur, l'autre aux

autres contrôleurs.

L'interface MCSI (maintenance

channel serial interface) était gérée par des logiciels s'exécutant entièrement

sur l'URC. Ces logiciels étaient écrits dans un code 32-bits interprétés par un

driver spécialisé. Un système d'exploitation SPOS incluant un moniteur de

travaux et s'adressant à la console système et à des fichiers sur cassette

(ultérieurement) sur diskette se chargeaient de l'initialisation et de

l'exécution des programmes de test du processeur.

L'interface

de service des autres contrôleurs elle était visible des logiciels spécialisés

s'exécutant dans le processeur central (programmes de T&D)

Le MIOS et

certains drivers nécessaires à l'initialisation du système étaient résidents sur

des PROM. Le reste des drivers résidaient en mémoire DRAM. Les programmes de

diagnostics n'étaient alimentés depuis une mémoire secondaire (initialement une

cassette de bande magnétique remplacée par une diskette 8 pouces sur URC-E) en

mémoire DRAM de l'URC. La taille de cette mémoire était de 32 K octets (étendue

plus tard à 64 K octets en URC-E).

L'URC était également un frontal

pour les lignes de télécommunications et les terminaux en local –dont la console

Terminet 300. Un multiplexeur d'adapteurs de lignes, appelé UCLA

(universal communications lines adapter) était connecté à l'URC via

l'interface DAI. C'était un tiroir comprenant jusqu'à 15 terminaisons de lignes

qui étaient soit de type synchrone (VIP ou BSC), de type asynchrone (TTY) ou

enfin de type HDLC. Les modems fournis à l'épqoue par les PTT nationaux étaient

dans des armoires distinctes et reliés au tiroir UCLA par des câbles série. La

plupart des fonctions de gestion des protocoles de communications étaient

remplies par du firmware URC, appelé MLA (multi-line attachement). Seul

la mise en série des bits depuis (ou vers) l'interface caractère était à la

charge du matériel de l'UCLA. L'adapteur de lignes comportait en outre une

mémoire tampon de deux caractères.

A chaque ligne correspondait un canal

logique, ce qui permettait à certains programmes (ex: émulateurs)le contrôle

exclusif de leurs protocoles.

L'approche adoptée par le

logiciel GCOS-BTNS (Basic Terminal Network Support) fut de charger dans

l'URC des programmes canaux en

boucle, synchronisés par des attentions avec le logiciel du

central.

L'introduction du 64DPS en 1979 s'accompagna de versions légèrement modifiées des contrôleurs MSC-E et MTC-E, qui différaient de leurs prédécesseurs par une simplification due à l'abandon des dispositifs de migration de la génération antérieure. L'URC-E recevait de nouvelles connections et sa fonction processeur de service était sensiblement améliorée par la substitution d'une diskette 8 pouces au lieu des cassettes de bandes magnétiques utilisées précédemment.

| appareil | nature | Lieu de

conception |

Lieu de

fabrication |

conception de l'électronique des appareils |

| PR |

imprimante | Data

Products |

Belfort | |

| PR46 |

imprimante à

bande |

Belfort | Belfort | Belfort |

| CR300 |

Lecteur cartes | Belfort | Belfort | Belfort |

| CR96 |

Lecteur cartes 96

col |

Pregnana | ||

| H-234X |

Lecteur/trieuse

de chèques |

Oklahoma City | Oklahoma |

Paris |

| Diskette | Diskette

8" |

Toshiba |

Toshiba |

Paris |

nouveaux appareils "unit

record" sur URC-E

DPS-7

Le DPS-7/x5 (P7G-CCR, Taurus) et le DPS-7/x0 (P7G, Leo) adoptèrent pour l'essentiel les mêmes systèmes périphériques que le 64-DPS. Une modification du câblage des canux (pour une réduction de coût) conduisit à introduire de nouveaux modèles de sous-systèmes fonctionnellement identiques à ceux de la génération précédente.

Après quelques considérations pour réimplanter l'URC en de

nouvelles technologies, il fut décidé de la conserver inchangée et de supporter

quelques périphériques nouveaux:

| appareil | nature | Lieu de

conception |

Lieu de

fabrication |

conception de l'électronique des appareils |

| STC |

Bandes

magnétiques |

Boulder |

||

| PR54 |

Imprimante à

bande |

Belfort |

Belfort |

Belfort |

La connexion de bandes magnétiques de bas de gamme d'origine STC (futur StorageTek) se fit par l'intermédiaire d'un adapteur spécial à l'URC, le MTA.

Un nouveau contrôleur de bandes magnétiques pour le DPS-7 fut conçu à la fin des années 1970 pour les bandes magnétiques PENA-30 de conception CII et qui offraient la fonctionnalité d'enregistrements GCR (group code recording) à 6250 bpi en plus des supports de la modulation de phase à 1600 bpi et du format NRZ à 800bpi. Ce contrôleur reçut le nom de ATP (Advanced Tape Processor) il fut conçu par les équipes des Clayes et mis en fabrication à Belfort.

En 1975, Honeywell en plus de son dégagement partiel de sa

filiale française, décida de fusionner son activité disques avec celle de

Control Data (CDC) en créant la compagnie MPI

(Magnetics Peripheral Inc) sous le contrôle majoritaire de CDC.

Honeywell-Bull possédait les usines de fabrication de disques en Europe,

héritées de Honeywell au moment de la fusion de 1970. L'usine de Heppenheim

(République Fédérale d'Allemagne) fut elle aussi apportée à MPI en échange d'une

participation de 10%? De CII-HB

dans MPI. Les activités disques d'Oklahoma City et de la région de Boston furent

relocalisées dans le Minnesota.

Honeywell (et en conséquence

CII Honeywell-Bull) se privaient de la poursuite à long terme d'une famille de

disques à l'interface propriétaire DLI, puisque MPI visait comme objectifs les

compatibles IBM et surtout les disques pour mini-ordinateurs pour lesquels ses

disques SMD avaient une position dominante.

CII-HB adoptera rapidement les disques SMD d'origine MPI pour ses lignes DPS-6, DPS-4 (level 62) et Level-61. Les perspectives d'évolution vers le DPS-7 de ces modèles et la recherche de coût réduits en entrée de gamme conduisirent à décider la réalisation d'un nouveau processeur de périphériques, le MSC-RV à l'interface SMD. Cette interface différait en effet sensiblement de l'interface étoilée DLI en présentant un bus de commandes et une étoile pour les transferts de données. La technologie du MSC-RV restait classique autour de la TTL-S, mais le moteur utilisa les processeurs en tranche 4-bits AMD 2901. Cependant, le firmware (support de l'interface PSI et des commandes GCOS7) ne supportait que de faibles modification, l'architecture (code d'instruction local) du PCP reprenant celle du MSC-E dont l'équipe CII-HB avait complètement acquis la maîtrise. Pour rester dans la perspective stratégique d'une offre de disques propriétaires, Honeywell avait obtenu de MPI que les disques à l'interface SMD soient légèrement modifiés pour ne pas être plug-compatibles avec les versions OEM.

Alors que la majorité des systèmes de bas de gamme restaient fidèles à la connexion des lignes de communications via l'UCLA de l'URC, sur les DPS-7 Leo, fut introduit le frontal de communication DSA, aussi appelé Datanet. Le Datanet (du point de vue matériel, un DPS-6) était lui aussi connecté à l'interface PSI par l'intermédiaire d'un adapteur conçu par les études des Clayes. Il réutilisait les connections de différents types de lignes présentes sur le DPS-6, son logiciel était entièrement conçu et développé par les équipes ex-CII des Clayes.

Comme sur la ligne GCOS-8, de grands clients de Bull commandèrent un adapteur PSI pour le Hyper-Channel de Network Systems Corporation, dans le but d'avoir une liaison canal à canal à grand débit pour interconnecter leurs grands systèmes Bull avec leurs machines Cray et IBM.

DPS-7000

La seconde génération de DPS-7 (Lyra) et la première génération de DPS-7000 (Ares) virent leur offre de périphériques complètement revue tout en continuant de supporter les anciens contrôleurs et appareils en parc.

Les années 1980 virent se briser l'équilibre économique établie dans la décennie précédente entre le constructeur dominant et le BUNCH. Ce dernier s'était en quelque sorte fédéré autour de Control Data pour le développement de disques magnétiques. L'IBM 3380 système à disques fixes ébranlait sérieusement la capacité de CDC-MPI à fournir des disques OEM aux clients IBM. Le marché des disques 14 pouces commençait à être concurrencé par des disques fixes moins encombrants de 9 pouces fournis par les constructeurs japonais et de nouveaux disques 5 ¼ pouces à de destination des micro-ordinateurs devenaient disponibles.

La ligne de produits DPS-7 entreprit de faire face à cette rupture de plusieurs manières:

A l'exemple de la ligne GCOS8, on envisagea la connexion de sous-systèmes complets IBM en réutilisant l'adapteur canal PSI-canal FIPS. Le canal IBM fut standardisé sous le nom de FIPS-60 par le comité de standards Fédéral américain. L'adapteur fit développé par IBM Poughkeepsie pour Honeywell Phoenix. Il fut testé sur DPS-7 et sous GCOS sur un sous-système IBM 3880, mais finalement non annoncé.

CII-HB avait commencé le développement de disques pour minis et micros, la famille Cynthia développée aux Clayes et à Belfort. Ces disques ne permettaient pas le maintien des enregistrements physiques de longueur variable CKD, à cause de l'absence d'une piste de synchro. Bull commença une longue et pénible conversion du logiciel GCOS7 au support (simultané) de deux formats de disques. Finalement, le projet Cynthia fut abandonné et les secteurs fixes (projet FBO fixed block organization) furent finalement introduits avec des disques 5 ¼ pouces à l'interface SCSI sur le DPS-7000 de bas de gamme.

L'offre principale de Bull sur DPS-7000 fut finalement celle de disques 9 pouces d'origine Hitachi (FSD500) puis Fujitsu regroupés en unités de 4 disques à l'interface SMD associées à un contrôleur MSC-4. Ce MSC-4 (toujours en format CKD) fut modifié en 1986 pour être connecté à une version "streaming mode" du canal PSI (PSI-S).

L'offre d'imprimantes fut modifiée par l'introduction de la ligne Mathilde, imprimante non-impact magnétographique, performante et flexible mais de coût élevé: la commande de l'imprimante était assurée par un mini-ordinateur DPS-6 capable d'une impression off-line et par la connexion d'imprimantes de bas de Gamme Data Products. L'imprimante Mathilde était connectée au DPS-7 par l'intermédiaire d'une liaison série ou plus tard d'une liaison Ethernet. Les imprimantes non-impact, développées à l'origine Bull-Belfort, firent l'objet d'une externalisation dans la société Nipson Printing Solutions.

L'offre mini-ordinateur de Bull s'orienta dans les années 1980 vers des solutions standard de l'industrie avec l'abandon planifiés des DPS-6 et DPS-4 (sous contrôle d'un Honeywell encore hors du contrôle de Bull, mais tenté par un désengagement de l'informatique) pour des solutions UNIX installées sur des microprocesseurs fournis par l'industrie américaine. L'adoption de la SM-90 et les perspectives de développement de Motorola en France mirent le MC68000 au centre de ces solutions standard. Il devint naturel à Bull de cesser le développement de mini-processeurs spécialisés et "propriétaires" pour adopter aussi le 68000 comme micro-contrôleur de périphériques et plus particulièrement pour le bas de gamme DPS-7. L'utilisation d'un bus standard (ce que n'était pas celui de la SM-90) s'imposait et il fut fait le choix d'un bus 32-bits de Intel le Multibus II.

C'est sur cette base qu'une nouvelle génération

d'entrées-sorties vit le jour vers 1985, avec une introduction initiale sur

DPS-7000 Ares bas de gamme. Cependant, si la base de l'architecture –et en

conséquence le coût de la conception et de la fabrication des puces - était

devenu celle du reste de l'industrie, l'architecture micro-logiciel restait

essentiellement celle expérimentée pendant des années, si bien que les plaques

logiques restèrent, pour la plupart,

spécifiques à Bull. Le micro-logiciel de plusieurs contrôleurs de la

précédente génération fit l'objet d'un portage sur MC68010.

Pour les nouveaux périphériques, les réticences initiales de

l'engineering sur la fiabilité de l'interface SCSI s'estompèrent devant

l'avantage de prix offerts par ce type de disques.

Les contrôleurs nouveaux suivants furent développés par Bull dans la seconde moitié des années 1980:

Le micro-FEP reprenant la fonctionnalité du frontal Datanet. Ce micro-FEP évolua vers un nouveau frontal puissant vendu sous le nom de MainWay sur l'offre réseaux de Bull.

Le MTC-G offrit les dérouleurs de bande Keystone de CPI (groupe Control Data) capables de lire des bandes standard PE et GCR, mais de débit inférieur au PENA-30. De fait, les bandes magnétiques n'étaient plus, dans les années 1980, utilisées que comme mémoire de sauvegarde des disque magnétiques.

Le SPA (Service Processor Adapter) reprenait les fonctions de l'URC-E -à l'exception de l'adapteur de communications MLA abandonné pour le micro-FEP - y compris les fonctions de maintenance du processeur et de plus offrait une interface réseau local Ethernet pour connecter un ou plusieurs micro-FEPs.

Un MSA développé en collaboration avec une firme britannique, servait d'adapteur de disques SCSI 8 puis 5 ¼ pouces.

Ces adapteurs étaient connectés directement par une interface Multibus II à l'IOC de Libra (le modèle d'entrée du DPS-7000) puis sur le matériel Vega.

Pour le haut de gamme, Bull s'orienta vers des sous-systèmes autonomes dotés de leur propre stratégie de traitement des erreurs et souvent dotés de caches de talle suffisante pour supprimer les contraintes temps réel des entrées-sorties.

La mode des "machines bases de données" dans les années 1980, conduisit Bull à entreprendre le projet APSS avec la compagnie Copernique, fondée par François Michel, un ancien directeur de Bull-SEMS. Ce projet échoua car Copernique basait son offre sur des disques à l'interface SCSI, tandis que Bull insistait pour utiliser des disques à l'interface IPI (normalisée, mais supportée presque exclusivement par un CDC moribond).

Finalement, l'offre disques comporta un serveur CDA7 d'origine EMC² au DPS-7 recevant des disques SCSI et incluant un cache pour les enregistrements de données sur disque.

Les mémoires à cartouches magnétiques organisées en une librairie on-line développées par StorageTek furent aussi connectées à quelques systèmes de haut de gamme DPS-7000 Auriga. Plusieurs versions de ces systèmes de librairie se succédèrent au cours des années 1990.

Les lignes de communication furent connectés au frontal Bull MainWay, lui aussi développé sur une architecture MC-68000, relié au central par une interface fiber-channel ou Ethernet.

Pour être complet, on notera que processeur de service de la famille Auriga fut un micro-ordinateur Intel 486 sous Windows relié à un adapteur de maintenance (lui même à base de microprocesseur 386) située dans l'armoire du central.

Cette évolution se termine par l'utilisation d'une plate-forme de serveur Intel sur Diane qui donne au système GCOS7 accès à tous les périphériques et drivers présents et futurs disponibles sur les serveurs à base de micro-ordinateurs à l'interface PCI ou ses successeurs.