| Unit Record Processor

Une partie importante de l'architecture du Level

64/DPS-7 est dissimulée dans un mini-ordinateur auxiliaire formellement connu sous le nom

de processeur de périphériques Unit record. On emploiera ici le nom engineering, moins

promotionnel, mais bien plus utilisé d'URC (Unit Record Processor).

Lorsque des systčmes possédant plus d'une URC ont été

commercialisés, l'URC principale -celle connectée au canal de maintenance du processeur

central- a reçu le nom de SURP System Unit Record Processor. Les

différences opérationnelles entre le SURP et les URC ordinaires sont décrites dans les

paragraphes initialisation et maintenance

ci-dessous.

© 2002,2003 Jean Bellec

- Histoire

- Projet

- Architecture

- Technologie

- Micro-Logiciel

Histoire de l'URC

Origine:

A une revue du programme Charlie ŕ la fin de 1967, John Haanstra

suggéra l'adoption d'un mini-ordinateur pour effectuer le contrôle des entrées sorties.

A cette époque, ni Bull-GE, ni General Electric ne disposaient de matériel semblable -

le Datanet-30 était construit en une technologie obsolčte et son successeur le Datanet

355 était plus puissant, mais trop cher pour ętre utilisé ŕ plusieurs exemplaires sur

un systčme moyen.

L'équipe de Georges Lepicard avait déjŕ commencé ŕ faire les spécifications d'un

contrôleur de lignes de télécommunications micro-programmable qui évolua au cours de

l'année 1968 en ce qui devint plus tard connu sous le nom de URC (Unit Record

Controller).

La raison pour laquelle ce mini-ordinateur s'appelle Unit Record, est que Bull-General

Electric avait obtenu la "mission" des appareils Unit Records (appareils ŕ

cartes et imprimantes) pour le groupe, les appareils étant confiés ŕ Belfort, les

sous-systčmes NPL devant ętre conçus ŕ Paris dans le Medium Systems Department.

Cet URC, essentiellement optimisé pour le systčme moyen -futur Level 64- devait servir

aussi de sous-systčme unit record pour le haut de gamme et l'établissement parisien ne

faisait pas trop mystčre de son souhait de voir utiliser cette plate-forme comme un

processeur de bas de gamme, réglant ainsi un vieux compte avec leurs amis transalpins.

Le systčme en cours de conception n'était pas -en principe un systčme transactionnel-

mais il semblait désirable de le doter d'une configuration minimale de ligne de

communications (support de Teletypes et de ligne haute vitesse 4800 bps pour le remote

batch). Un systčme doté d'un processeur 16-bits fonctionnant ŕ une

fréquence de 6 MHz -celle du CPU- devait ętre capable de multiplexer un ensemble

d'appareils ŕ cartes, une imprimante et 16 lignes ŕ 110 bps en plus d'une ou deux lignes

remote batch, moyennant la dotation de mémoires tampon adaptées.

L'idée d'un processeur de maintenance faisant les diagnostics off-line de la logique du

processeur principal et capable de suppléer aux procédures manuelles d'initialisation du

systčme se fit jour en 1969-1970 et comme ce processeur était susceptible d'utiliser

off-line les périphériques unit record, il apparut judicieux de combiner ces fonctions

avec celles de l'URC. Le seul appareil manquant était une mémoire de masse permanente

pour laquelle l'utilisation des cassettes de ruban magnétique était -en 1970- une

solution acceptable, qui devint encore plus attrayante lorsque les augures annoncčrent

que ce media pouvait remplacer avantageusement la carte perforée comme véhicule de

saisie de données. |

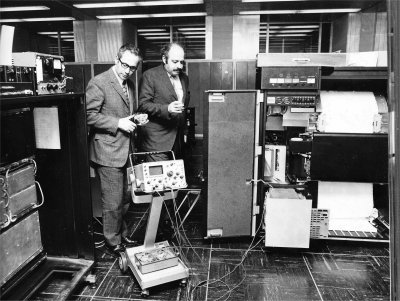

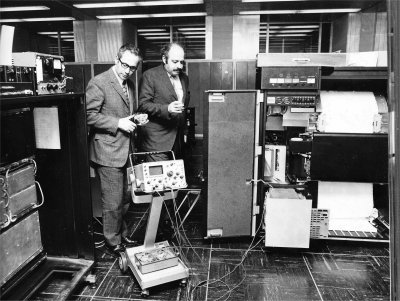

Projet URC

La conception et la réalisation de l'URC a été réalisée dans

la division Périphériques de la direction hardware des Systčmes Moyens de

Honeywell-Bull sous l'autorité de Henri Verdier.

Les outils logiciels étaient développés dans la division

Software de la Direction hardware, initialement dirigée par Michel Rocher, puis par

Jean-Jacques Pairault.

Les "device adapters" de périphériques étaient

conçus par l'équipe de Henri Verdier et réalisés par les constructeurs des

périphériques -ils se trouvaient dans l'armoire du périphérique et packagés avec

l'électronique analogique spécifique de celui-ci, ŕ l'exception des adaptateurs de

communication (MLA) , intégrés dans un tiroir voisin de l'URC, réalisés par l'équipe

de Jean Akriche chez Henri Verdier. |

| Architecture de l'URC

Bien que l'URC ait été conçu comme un mini ordinateur ŕ usage

général, on n'avait jamais envisagé que sa base architecturale soit directement

programmable par l'utilisateur final. Lorsqu'on a envisagé son utilisation comme

processeur de bas de gamme, l'"interior decor" considéré devait ętre un code

d'instructions compatible avec celui du 64 (aligné octet, instructions de longueur

variable...) interprété par du "firmware" et non le décor natif offert par le

matériel (machine mot de 16-bits, adressage limité ŕ 64KB, 2 registres de base -

un pour le code, l'autre pour les données-). On a donc appelé "firmware de

l'URC" le logiciel en mode natif, dont une partie, celle du "bootstrap", et

les pilotes des périphériques de base était réalisé en PROM.

L'URC comprenait un processeur, une mémoire DRAM et des

adaptateurs (1 ou 2 adaptateurs de canal PSI -liaison avec le processeur central,

adaptateurs de canaux DAI -liaison avec l'électronique des périphériques).

Les canaux DAI étaient un standard Honeywell et identiques pour tous les périphériques

(parallčle sur 8-bits).

Les "device adapters" de communication étaient de types

différents: un adaptateur de lignes asynchrones regroupant 8 lignes ŕ basse vitesse avec

un double tampon d'un caractčre par ligne, un adaptateur de ligne asynchrone ŕ

"grande vitesse" , un adaptateur de lignes synchrones BSC puis plus tard un

adaptateur de ligne synchrone HDLC. Ces adaptateurs étaient échantillonnés par le

programme de gestion de lignes aussi appelé "MLA firmware". |

| Technologie de l'URC

La technologie était identique ŕ celle du

processeur principal Level 64 (mémoire MOS 4Kbits, technologie TTL 74N, packaging SP-10. |

| Micro-Logiciel

Inspiré de la conception du processeur du Level 64, un

"microprogrammed-OS" (MIOS) servait de systčme d'exploitation

de l'URC. Il s'agissait d'un micro-noyau qui, non seulement gérait les interruptions,

mais aussi assurait le dispatching des tâches et leur synchronisation au sein de l'URC.

Ce MIOS faisait partie de la partie réalisée en PROM et était par conséquent chargé

au début de l'initialisation de l'URC.

Les micro-tâches étaient les suivantes:

- le pilote du lecteur de cartes (code en PROM)

- le pilote du perforateur de cartes

- le pilote de bande perforée

- le pilote d'imprimante (PR71 et PR54)

- le pilote du canal PSI de liaison avec le processeur central (code

en PROM)

- le pilote de cassettes de bandes magnétiques (code en PROM)

- le pilote de la console (modčle pour le haut de gamme développé

ŕ Billerica)

- le pilote de lignes asynchrone TTY (console bas de gamme GE

Terminet 300 compatible TTY35)

- le pilote de la trieuse de chčques

- le programme de gestion des lignes de communication (MLA firmware)

- l'interpréteur du programme de maintenance

La structure de ces micro-tâches était rigoureuse, la partie

procédure était réentrante de façon ŕ pouvoir supporter le multi-tasking (ex: support

de plusieurs imprimantes) et se dérouler simultanément sous contrôle du MIOS

multiplexant le matériel entre ces micro-tâches (appelées micro-process). C'est ainsi

que le fonctionnement des lignes de communication pouvait ętre complčtement indépendant

et ces lignes allouées ŕ des "logiciels" différents dans le central ou l'URC.

A propos des pilotes, il faut noter que la lourdeur de la

distribution des "releases" du micro-logiciel (Basic System Release BSR)

conduisit le Département de Conception de Périphériques Unit Record de Belfort ŕ

réaliser des matériels rigoureusement compatibles avec des matériels antérieurs, męme

si le coűt et la fonction de ces appareils en différaient sensiblement (ex: lecteur de

cartes CR300 et lecteur de cartes Honeywell CR 1000).

Pour la liaison avec le processeur central, l'URC disposait du

canal PSI et d'un canal spécial de maintenance. Ce dernier servait ŕ lancer la

réinitialisation du central, ŕ accéder au contrôleur de mémoire centrale et ŕ

extraire le contenu des registres de l'unité centrale. Le pilote de canal PSI avait comme

fonction d'assurer la communication entre le logiciel du central (via le contrôleur

d'entrées-sorties du central et son firmware associé) avec les pilotes de contrôle de

périphériques. Il maintenait un ensemble de "subchannels", entités logiques

définissant des chemins de données (macroscopiquement asynchrones) entre les

"processes" du central et des fonctions logiques sur les périphériques.

Cet asynchronisme avait des limites dues aux fonctions "temps réel" du

sous-systčme d'entrées sorties. Ces fonctions pouvaient ętre réalisées, comme sur le

IBM S/360, en synchronisant les "programmes canaux" du central avec les

"interruptions" des entrées-sorties. Pour les opérations plus contraignantes,

l'URC permettait au programmeur du central de prédéfinir des actions se déroulant dans

l'URC (actions sur caractčres spéciaux de communications, actions sur les trieuses

de chčques). Ces actions étaient soit définies par des déclarations transmises au

programme de gestion de lignes de communication, soit par la génération d'un programme

compilé pour la lecture et le tri de chčques. |

| Attachement de Périphériques La spécification de l'URC, faite ŕ un moment oů la logique des

devices adapters était coűteuse, n'avait pas prévu que ces devices adapters

enregistraient le type d'appareil qu'ils reliaient ŕ l'URC. Ainsi, il n'y avait pas de

possibilité de reconnaissance automatique des appareils au moment de l'initialisation

(Fonction Plug and Play).

Les "Device Adapters" spécifiques de chaque

appareil étaient connectés ŕ l'URC par une interface standard DAI (également utilisée

sur Level 62 et Level 66). Cette interface parallčle sur un octet était directement

contrôlée par les micro-programmes de l'URC.

lecteur de cartes

- PCR80

Le lecteur de cartes perforées PCR80 était de conception Honeywell, mais sa fabrication

fut transférée ŕ Belfort en 1972.

lecteur-perforateur de cartes

- PCP80

Le perforateur de cartes PCP-80 utilise la męme base mécanique que le PCR80.

lecteur de documents

- LD1

Le lecteur de documents OCR ou MICR de fabrication Bull Belfort avait déjŕ été commercialisé

sur les GE-100 et GE-400. Il fut reconnecté sur le Level-64

imprimante

- PR71

Les imprimante ŕ bande d'impression PR46 et de la PR71 furent les premičre

imprimantes Bull ŕ disposer d'un ensemble de caractčres interchangeable par l'opérateur

du client. La bande était auto-reconnaissable par le pilote de l'URC.

Ces imprimantes possédaient un mécanisme de saut de papier variable suivant un

mécanisme firmware émulant le fonctionnement des bandes pilotes. Cette émulation se

faisait dans le pilote de l'URC et pouvait ętre rechargé par le logiciel GCOS.

- H112

L'imprimante Honeywell H-112 fut essentiellement utilisée pour la reprise des

systčmes récents Honeywell 3200.

La définition de l'attachement imprimante posa des

problčmes particuliers dus ŕ l'existence d'une phase off-line, l'avance du papier.

Cette avance était lancée par le micro-programme ŕ la fin du transfert de données dans

le tampon ligne de l'imprimante, mais la fin du saut de papier n'était détecté que

lorsque le microprogramme se préoccupait de l'envoi de la ligne suivante. Un incident

mécanique d'avance papier était donc détecté aprčs que le logiciel du central ait

reçu le signal de transfert de données. Dans le cas oů le logiciel n'avait pas prévu

de point de reprise au niveau de la page, ce problčme risquait de provoquer un message

d'erreur sur l'état d'impression "LINE MAY BE LOST"

trieuse de cheques

- H234X

La connexion du lecteur-trieuse de chčques (modčle MICR ou OCR) posait des problčmes

que la plupart des autres appareils unit-record. Les critčres de sélection (champ des

données, codage, type...) de la case de réception normale des chčques étaient sous-la

dépendance du programmeur d'application. De plus, la trieuse de chčques rencontrait des

cas d'impossibilité de lecture devait provoquer la sélection en case rebut sans ralentir

le rythme de la machine. La lecture des chčques ne devait s'arręter que dans le cas de

case d'alimentation vide, de case sortie pleine ou de bourrage.

bande perforée

Multi-Line adapter (MLA)

Le MLA est composé de deux composants: un composant

matériel l'UCLA (Universal Communication Lines Adapter) panier (card cage)

recevant une carte de liaison avec l'URC (Common Board) via l'interface DAI et jusqu'ŕ 15

adaptateurs de ligne, et un composant micrologiciel l'"attachement MLA".

Plusieurs modčles d'adaptateurs de ligne ont été offerts (l'adaptateur de ligne

asynchrone possédant une horloge bit programmable, l'adaptateur de lignes synchrones et

l'adaptateur HDLC , ces derniers étant synchronisés par le modem). L'interface entre

adaptateur et UCLA est parallčle sur un caractčre, l'interface entre adaptateur et modem

est du type série. Les adaptateurs pouvaient indifféremment ętre utilisés via modem ou

en connexion locale ŕ courte distance.

L'attachement MLA reconnaît chaque caractčres de

contrôle, vérifie leur parité -s'il y a lieu-, interprčte les caractčres de contrôle

de bloc et vérifie les contrôles d'intégrité (CRC) selon les protocoles de

transmission, effectue -éventuellement- une traduction (ex: ASCII<>EBCDIC), et

regroupe le contenu pour une transmission par blocs ŕ l'unité centrale. En outre,

l'attachement MLA interprčte les caractčre de Break qui interrompent la

transmission et informe le central par une "attention" spécifique, pouvant

interrompre le déroulement du programme canal. A chaque ligne est associée 1 ou 2 logical

channels (selon half-duplex ou full-duplex).

Les options du MLA sont le mode TTY (avec support de bande perforée) , le mode Honeywell

VIP (avec option de multi-point), le mode IBM BSC utilisé essentiellement en "remote

batch", le mode HDLC X25 (compatible IBM SDLC). Un mode Télex 5 moments, code Baudot

a été offert mais n'a gučre eu d'applications. Essentiellement pour les pays nordiques

un support de l'interface de commutation automatiques de circuits X21 a également été

offert sur URC.

Presque tous les systčmes avec URC ont eu la console

systčme connectée via le MLA. Seuls font exception des systčmes de haut de gamme ayant

reçu un adaptateur spécial pour une console conçu ŕ Boston ŕ base de CRT. La console

la plus répandue avant 1981 fut le General Electric Terminet 300 (compatible TTY). Il a

été ensuite remplacé par un écran du type VIP, utilisé par GCOS d'abord en mode TTY,

puis en mode plein écran.

Attachement de Canaux

Canal PSI

L'interface avec le canal PSI était une interface

parallčle sur un octet. L'URC pouvait recevoir un second canal PSI permettant de la

partager entre deux unités centrales. Les sous-canaux correspondant aux périphériques

étaient partagés statiquement (ŕ la génération du firmware) entre les deux appareils

ce qui limitait l'intéręt de la double connexion. Elle ne fut gučre utilisée que pour

connecter l'ensemble des périphériques ŕ l'une ou l'autre unité centrale, jouant

un rôle identique ŕ celui d'un switch de canaux PSI utilisé sur les autres

sous-systčmes périphériques.

Canal de maintenance

Le CPU du central (et les autres contrôleurs de

périphériques) était connecté via l' interface série MCSI. |

| Initialisation

La mise au point initiale du systčme Level 64 commença ŕ Paris

Gambetta en avril 1972. Les contrôleurs de bandes magnétiques et de disques étaient

développés ŕ Billerica et n'étaient pas encore disponibles. Aussi, le systčme central

et sa mémoire devaient ętre initialisés ŕ partir d'un deck de cartes perforées lues

dans l'URC. Cette fonction de durée assez longue (de l'ordre de 15 minutes) fut utilisée

seulement avant la connexion du MSC et du MTC. En fait, le lecteur de cassette et son

"device adapter" (produit par Honeywell Italia) n'étaient pas non plus

disponible, ce qui fait que le paquet de cartes -en mode binaire- émulait la future

cassette du point de vue fonctionnalité d'utilisation. la cassette inversement émulera

le lecteur de cartes en adoptant des blocs de 120 octets (960 bits) .

A noter que le systčme prototype du Level 64 possédait une mémoire ŕ tores

magnétiques comme aussi le prototype de l'URC, bien qu'il soit prévu d'utiliser des

mémoires DRAM dčs le début (seul le premier prototype était équipé de mémoire ŕ

tores).

On décrira ici, l'initialisation des prototypes complets ŕ

partir de la cassette.

A la mise sous tension du matériel, l' URC initialisait sa mémoire et effectuait des

auto-tests (les POST d'aujourd'hui) de son processeur et de sa mémoire depuis ses

"microprogrammes" en PROM. Le MIOS commençait le chargement et l'initialisation

des micro-processes dont le code était résident en ROM et la mémoire de travail (dans

la mémoire vive de l'URC) auto-initialisée. Aprčs cela, il chargeait le

"firmware" d'initialisation depuis la cassette située dans le lecteur, puis sur

le contrôle de cet "attachement d'initialisation", il lisait depuis le cassette

le "firmware" du processeur principal destiné ŕ s'exécuter depuis la

mémoire centrale vive. Ensuite, le processeur principal exécute un chargement du premier

"logiciel" normalement le System Initialisation Program SIP.

Une alternative au SIP -chargée le plus souvent depuis bande magnétique-

est le logiciel de tests fonctionnels élémentaires du processeur principal (OPELs).

Le rôle du SIP consiste ŕ examiner la configuration du systčme contenu dans des

tables logiciel (SRT System Resource Table), de charger le "firmware"

correspondant ŕ ces tables dans le sous-systčmes périphériques et en particulier dans

l'URC et de lancer définitivement la configuration opérationnelle. Il constitue aussi la

table de ressources effectivement disponible au systčme d'exploitation GCOS (SRST)

terminant ainsi le processus d'initialisation.

En fonctionnement normal opérationnel, l'initialisation a lieu

depuis disque; le "boot-record" est logé sur ces média au lieu d'ętre sur

cassette. Mais le lancement des tests (POST) des contrôleurs et le choix du

périphérique d'initialisation reste commandé par l'URC -via l'interface de maintenance

des MSC ou MTC. Le SIP se charge dans la mémoire principale ŕ partir du

"boot-record" et les autres contrôleurs de périphériques sont initialisés.

"L'image" de la mémoire URC comprenant le support des périphériques

spécifiés dans la SRT est descendue ("downloadée" ) dans la mémoire URC

depuis la mémoire centrale via le canal PSI. Les micro-tâches de l'URC sont lancées et

les périphériques qui le doivent sont placés dans leur état initial par ces

micro-tâches.

Dans le cas oů le sous-systčmes disques -s'il n'y en a qu'un-

doit faire l'objet de vérifications (Tests et Diagnostics du sous-systčme et d'un

appareil), l'initialisation a lieu comme depuis disques, le systčme d'exploitation

chargé étant le SCP

Maintenance

Un arręt inopiné du processeur central (interruption au niveau 0

-déclenchée par l'interpréteur d'instructions 64 ou par le superviseur GCOS ou par un

time-out sur la durée d'une instruction) se traduisait par l'envoi d'une

interruption ŕ l'URC sur le canal de maintenance, interrompant les microprocessus en

cours.

Le bootstrap résident de l'attachement de maintenance interprétait cette interruption et

lançait l'attachement de maintenance complet écrasant d'autres attachements de l'URC, ŕ

l'exception de la cassette, de la console et de l'imprimante. Cet attachement comprenait

l'interpréteur du décor processeur de maintenance et l'ensemble de drivers disponibles

ŕ l'initialisation.

Dans ce décor -un sous-ensemble réduit du décor GCOS62-

étaient écrits un mini-systčme d'exploitation MPOS 'maintenance panel operating

system" et un certain nombre de commandes interprétant les données entrées par

l'opérateur ŕ la console du systčme, telles que DUMP sur l'imprimante, DUMP registres

du CPU sur la console, etc...MPOS peut accéder ŕ plusieurs "devices" de l'URC,

notamment la console, la cassette et l'imprimante. L'accčs ŕ la cassette permettra de

créer des commandes non résidentes.

Génération

La programmation de tous les produits liés ŕ l'URC fut faite

jusqu'aux années 1980 sur des outils tournant sous GCOSIII sur GE-635, puis sur H-6000

dans les locaux de Bull. Il était, ŕ l'époque, considéré comme stratégique que ni

les filiales, ni ŕ fortiori les clients eussent une quelconque de connecter des appareils

non-Bull au systčme 64. La modularité de l'architecture permettait cette exclusion au

prix d'une complexité logistique non négligeable La distribution des Basic System

Release (ensemble des micro-logiciels et des outils logiciels appropriés) était

distribuée comme du "hardware" par l'usine d'Angers.

Le langage d'écriture du firmware de l'URC était un

macro-assembleur. Lorsque le processeur de l'URC devint un 68000, le langage C remplaça

l'assembleur.

URC vs Front-End Processor

Datanet-2000

Le Datanet-2000 était un processeur frontal de communications

développé par Honeywell pour la série H-200/2000 ŕ base du mini-ordinateur H-516. Pour

reprendre la base de clientčle H-200 par le Level 64, il fut décidé de connecter ce

frontal sur un canal PSI. L'existence de ce produit contribua ŕ diminuer la pression pour

le développement de l'URC-MLA vers le haut.

Commutateur d'interface DAI

Ce switch permettant de connecter un appareil (par exemple une

imprimante) ŕ deux URC fut construit. Il ne possédait pas de support systčme et son

action nécessitait la réinitialisation du systčme auquel était reconnecté l'appareil. |

Notes

PROM ou ROM.

les premičres réalisations furent faites en utilisant des PROM dont il était

nécessaire au fabriquant de semi-conducteurs de fournir le masque de métallisation

externe. Cette procédure -outre son prix élevé avait l'inconvénient d'un temps trčs

long entre la correction d'un bug et le remplacement du chip défectueux en clientčle.

Elle entraîna la création d'une "zone de patches" situés ne mémoire vive

dans laquelle étaient placés le contournement du problčme au prix d'un certain

ralentissement.

A l'époque des années 1970, les PROM étaient plus rapides que

les DRAM dans un rapport de 3. La DRAM posait de plus des contraintes de rafraîchissement

qui interrompaient le déroulement des micro-processus temps réel. L'architecture du

"firmware" URC devait ętre trčs rigoureuse pour minimiser l'impact des

corrections sur les performances.

Plus tard -sur l'URC-E-, des EPROM modifiables en usine par CII-HB et plus rarement

en clientčle remplaceront avantageusement les PROM.

Attachement de URC.

Mot utilisé par développeurs et commerciaux pour désigner les

"programmes se déroulant" sur l'URC sous-contrôle du MIOS. Ces programmes

occupent une certaine place mémoire, sont normalement relocatables et peuvent dans

quelques cas comporter des "overlays". Selon la configuration, ils peuvent ętre

multi-tâches (multi-thread)..

SCP et SIP

Le Support Control Program (SCP) est un systčme d'exploitation primitif permettant

l'exécution de travaux individuellement lancés par l'opérateur, soit un enchaînement

séquentiels de travaux. Il n'offre pas de support de multi-programmation, permet le

multi-tâches (défini statiquement). Il fut utilisé comme support de la premičre

version de l'émulateur GE-100 sur Level 64 et resta utilisé comme support des tests et

diagnostics "stand-alone" permettant les diagnostics de sous-systčmes disques

et de discriminer pannes du central et problčmes logiciels de GCOS.

A l'origine conçu comme un travail (job step) séparé sous SCP, l'initialisation

du systčme fut ensuite combinée avec le code de SCP, l'ensemble fut renommé System

Initialization Program (SIP). cette intégration réduisait de maničre significative la

durée de la phase de lancement de GCOS.

|

|

Unit

Record Processor

An important part of the architecture of

Level 64/DPS-7 is hidden inside a auxiliary minicomputer formally known

as Unit record Processor. We will rather use the engineering name of Unit

Record Controller that went more used as URP.

When systems with more than one URC were sold, the

main URC -that connected to the processor service interface- was named SURP System Unit

Record processor. Operational differences between SURP and other URC are described in

initialization end maintenance paragraphs hereunder.

© 2003 Jean Bellec

- History

- Project

- Architecture

- Technology

- Firmware

The URC History

Origin:

During a design review of project Charlie, end of

1967, John Haanstra suggested to adopt a minicomputer to handle the I/O of the system, to

limit the amount of exotic hardware to control peripherals. At that time, neither Bull-GE

nor General Electric had a computer suitable for those needs. The Datanet-30 front-end had

an obsolete technology and its successor, the Datanet 355, was more powerful but too

costly to be used at several items in a medium system.

George Lepicard's team, in Paris, had started the design of a communications multi-line

controller, microprograms controlled in 1967. This design evolved during 1968 to become

the URC (Unit Record Controller).

The name is in relation with a"mission" for Unit Records (punched card devices

and printer) allocated to Bull-GE and particulary its Belfort plant. The unit reocrd

subsystems were to be designed by Paris Medium Systems Department.

The URC was essentially optimized for the medium system -that eventually became Level 64-

but was also intended for the higher models and the Paris technical establishment wished

that this platform be also used as an entry-level processor for NPL, an intent that was

seen as a revenge on their trasalpine rivals.

The marketing target for the system was essentially batch (based on unit reords and

sequential files) , but the emergence of transaction systems provoked the addition of a

minimal set of communications lines (Teletype support and 4800 bps "high speed"

remote batch link used both as downwards and upwards link).

Using the appropriate buffers, the subsystem equipped with a 16-bits processor at 6 MHz

(same frequency as the main 32-bits CPU) should be able to multiplex a set of card

devices, a printer and 16 110bps lines (and a couple of faster lines).

The idea of a maintenance processor to esecute

off-line dianostics of the main processor's logic and able to automate system

initialization procedures went to light in 1969-1970. As this maintenance processor had to

use some unit record devices (card reader and printers) it appeared desirable to combine

those functions with those the URC. There was still a missing device, that of a bulk

storage device. The use of magnetic tape cassette (Philips audio format) seemed in 1970 a

solution, conforted by the expert prediction that such a media will be used as punched

card replacement for data entry. |

| URC Project

The design and implementation of the URC were done in

the Peripheral Division of Medium Systems Department, within the Hardware Direction. Henri

Verdier was in charge of this division.

Software tools were developed in the software

division of the same hardware direction that was initially headed by Michel Rocher, then

by Jean-Jacques Pairault.

Peripheral Devices Adapters were designed in Henri

Verdier's division, but generally implemented by peripherals manufacturers (Belfort and

Italy). They were packaged with the peripheral specific analog components. The

communication adapter (MLA) was packaged in a rack closed to the URC rack. It was

developed by Jean Akriche's team in Henri Verdier's organization. |

| URC Architecture

While the URC was deigned as ageneral purpose

minicomputer, it was never envisioned that its processor architecture was directly known

and programmed by an end-user. When it was envisioned to be used as a low-end processor of

the line, the "interior decor" was to be an instruction set identical or

compatible with that of 64 (byte aligned, variable length instructions...) interpreted by

"firmware" and not the native decor offered by the hardware (words of 16-bits,

addressability limited to 32K words, 2 bases registers -one for code, the other for data).

The native software using the hardware architetcure was named "URC firmware",

a part of which the "bootstrap" and some peripherals drivers being

implemented in PROM as in present microprocessor BIOS.

The URC included the processor, a DRAM memory and

adapters (one or two PSI channel adapters -connection with the CPU(s)-, several identical

DAI adapters -connection to the peripheral electronics). DAI channels were a Honeywell

standard featuring a 8-bits parallel interface, data transfer one byte at a time were

under the controller firmware control (URC for Level64).

The "device adapters " for data

communications, implemented in same frame as URC were in different models: an adapter for

asynchronous lines grouping 8 low-speed lines, each with a double buffer of one character

and a detection of start-stop pulses, an adapter for a high-speed asynchronous line,

a BSC synchronous line adapter and later a HDLC synchronous line. Those adapters were

sampled by the communications driver program in the URC also named "MLA

firmware". |

Technology of URC

The technology was identical to that of the main

Level 64 processor (MOS DRAM memory of 4Kbits per chip, switching components TTL 74N, SP10

Bull designed packaging). |

|

| URC

Firmware

Based on the design of the Level-64 processor

micro-kernel, a microprogrammed-OS (named MIOS) was the operating system

of the URC. That microkernel not only handles real time interrupts, but also did

dispatches drivers threads (micro-threads) and their synchronisation within URC. That MIOS

was implemented in PROM and did also tests and initializes the URC

Other micro-threads were:

- card reader driver (stored in PROM)

- card punch driver

- paper tape driver

- printer (PR71 and PR54) driver

- PSI channel driver (stored in PROM)

- magnetic tape cassette driver (stored in PROM)

- CRT console driver (developed in Billerica for high-end systems)

- asynchronous Teletype driver (for GE Terminet 300 console, TTY35

compatibme)

- check sorter driver

- communications lines driver (MLA firmware)

- maintenance language interpreter and driver

Those micro-threads were rigorously structured: the

procedure part was reentrant to support multi-tasking (e.g. to support two or more

printers) and operating entirely under the MIOS control that dispatched the hardware

resources between those "micro-processes". The behaviour of each communication

line could be completely independant allowing those lines to operate with different

software programs in the CPU or even inside URC.

Concerning drivers, it has to benoted that the

burden due to the distribution of firmware releases and related software(grouped under the

name of Basic Systems Releases) kead the Unit Record Peripheral Department in Belfort to

develop hardware models strictly compatible with models already in the field. Even when

cost and functionality differed, as in CR300 card reader and Honeywel designed CR1000),

the CR300 adapter hardware emulated perfectly the CR1000 one.

The link to the central processorand URC was made of

the PSI channel and a special maintenance chanel. The latter was used to trigger the CPU

initialization, to access the memory controller and to access the CPU registers. The PSI

channel driver had the role to allow the CPU software (usually GCOS) to access the unit

record peripheral drivers. It handled a set of subchannels, logical entities

seting data pathes (seen as asychronous) between CPU "processes" and logical

functions of peripherals.

Such an asynchronism had limits due to the real-time

functions of the I/O subsystem. usually, those functions were, as on IBM S/360, realized

by synchronizing the architectured channel programs with I/O interrupts. For more

time-dependent operations (handling of transmission control characters, control of

check sorter stackers), URC allowed the software programmer to predefine actions

within the URC. Those actions were either declarative tables sent to URC as initialization

of the subchannel. or just sending a precompiled URC program for check reading and

sorting. |

| Peripherals Attachment The design of the URC was made at atime where the logic part of devices

adapters was expensive; the specs were not including a memory of the device

characheristics attached to the URC. So, there was not a Plug and Play characteistics at

initialization time.

Device adapters were connected through a standard

interface, named DAI, that was common to Level 62, Level 64 and Leveal 88. This byte parallel

interface was directly accessible by URC microprograms.

punched cards reader

PCR80 was a device designed at Honeywell in the late

1960, its manufacturing was transfered in Belfort (France) in 19772

cards reader-punch

PCP-80 punch card used the same basic mechanism as PCR-80

document reader

The OCR or MICR documents LD1 manufectured by Bull Belfort

had been already sold on GE-100 and GE-400. It was also connected to Level-64 on the DAI

interface.

printer

- PR71

Band printers PR46 and PR71 were the first Bull printers with a character set

removable by the customer operator. The band carrying the character set was automatically

recognized by the URC driver.

Those printers had a paper skip mechanism emulating the pilot tape behaviour

located in the URC driver and reloadable by GCOS software.

- H112

The Honeywell H-112 printer on Level-64 was essentially used for delivery to

customers having recently installed Honeywell 200. It was used in H-200 emulation

mode and in native converted mode.

The definition of the printer attachment caused technical

problems due to the existence of an off-line phase, the paper movement phase. That phase

was triggered by URC microprograms after the transfer of data in the printer data

register, but the end of paper skip was notified only just before the microprogram

was beginning the next line printing. A paper skip problem was consequently detected after

CPU software had received the termination phase of the line. If that software had not

envisioned a checkpoint at page level, this problem might cause an "LINE MAY BE

LOST" message to be printed on the user listing.

check sorter

|

|