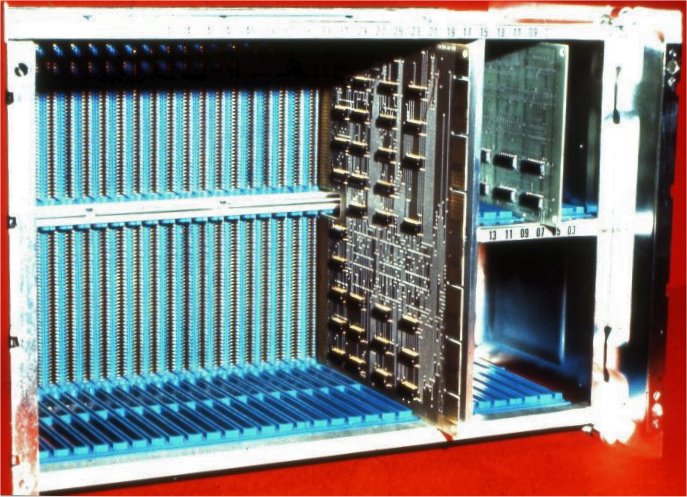

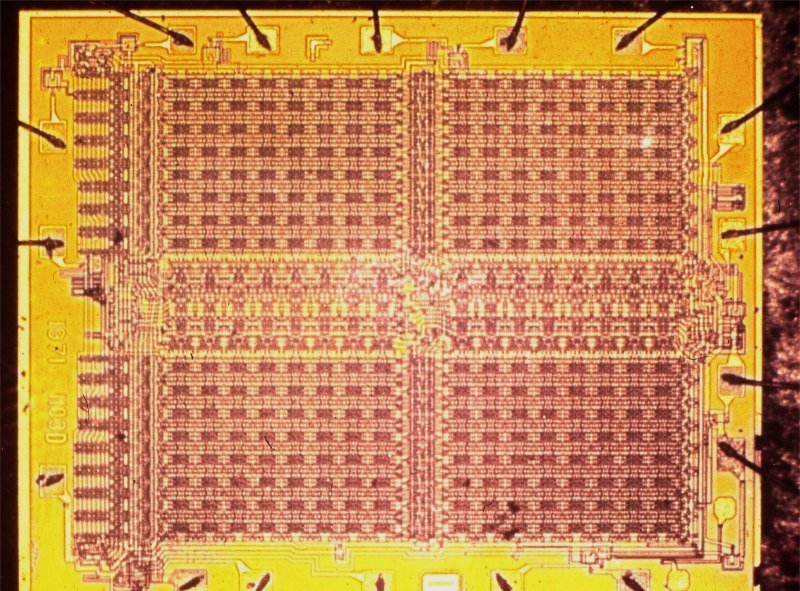

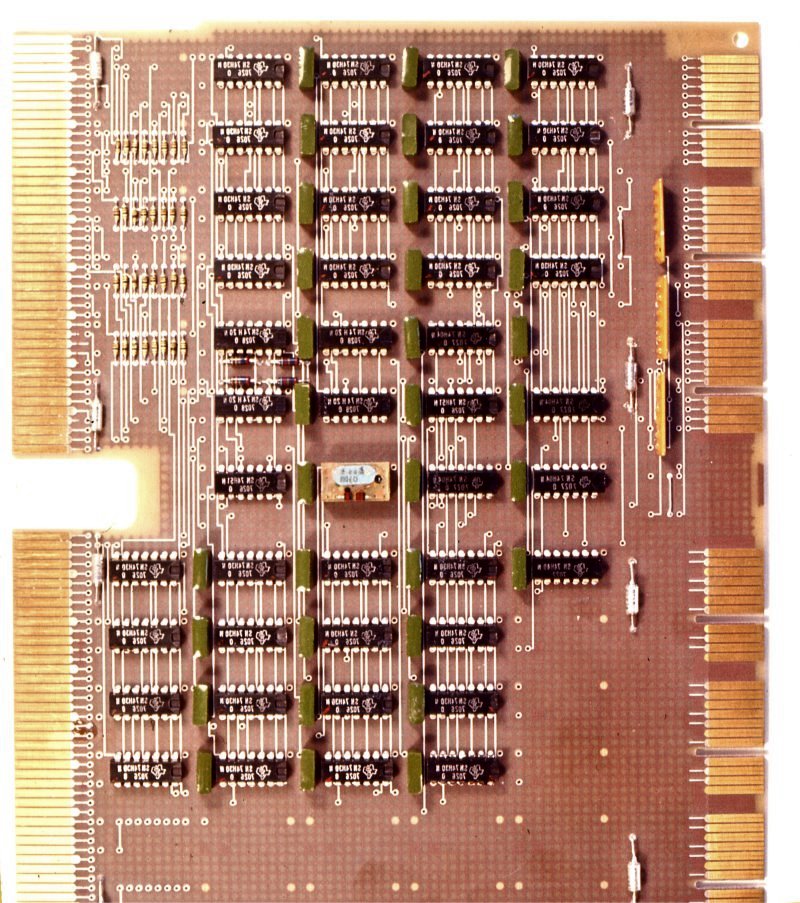

photographie d'un panier (cardcage) SP10 montrant le mixage de cartes SP10 simple et double format.

Level-64 et 64 DPS

Technologie

|

La technologie du 64 est basée

sur des circuits intégrés TTL, d'origine Texas Instruments 74N. A part les circuits DIL, le reste de la technologie est de conception et de fabrication Honeywell-Bull standardisée aux normes Honeywell. L'apport spécifique français est dans le connecteur SC-10 qui relie les plaques (SP10) au fond de panier. L'unité centrale du 64 comprend trois paniers recevant 90 plaques.

|

The Level-64 technology is

based on 74N TTL integrated circuits. In 1978, some circuits will be

replaced by 74S compatible circuits. A part those DIL circuits, the rest of the technology (printed boards, connectors, card cages, cabinets) are designed and produced by Honeywell-Bull at Honeywell standards. |

photographie d'un panier (cardcage) SP10

montrant le mixage de cartes SP10 simple et double

format.

photo d'un cardcage du processeur qui en contient de 5 à 8 selon

la configuration

photo Jean Bellec @2004 d'objets collectés par Dan Humblot

|

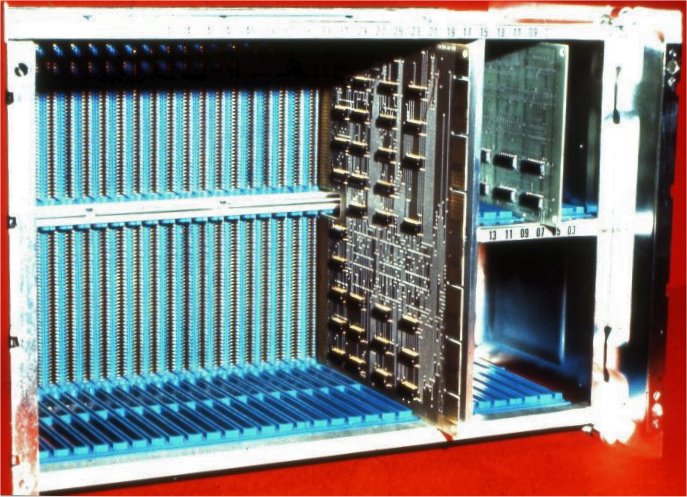

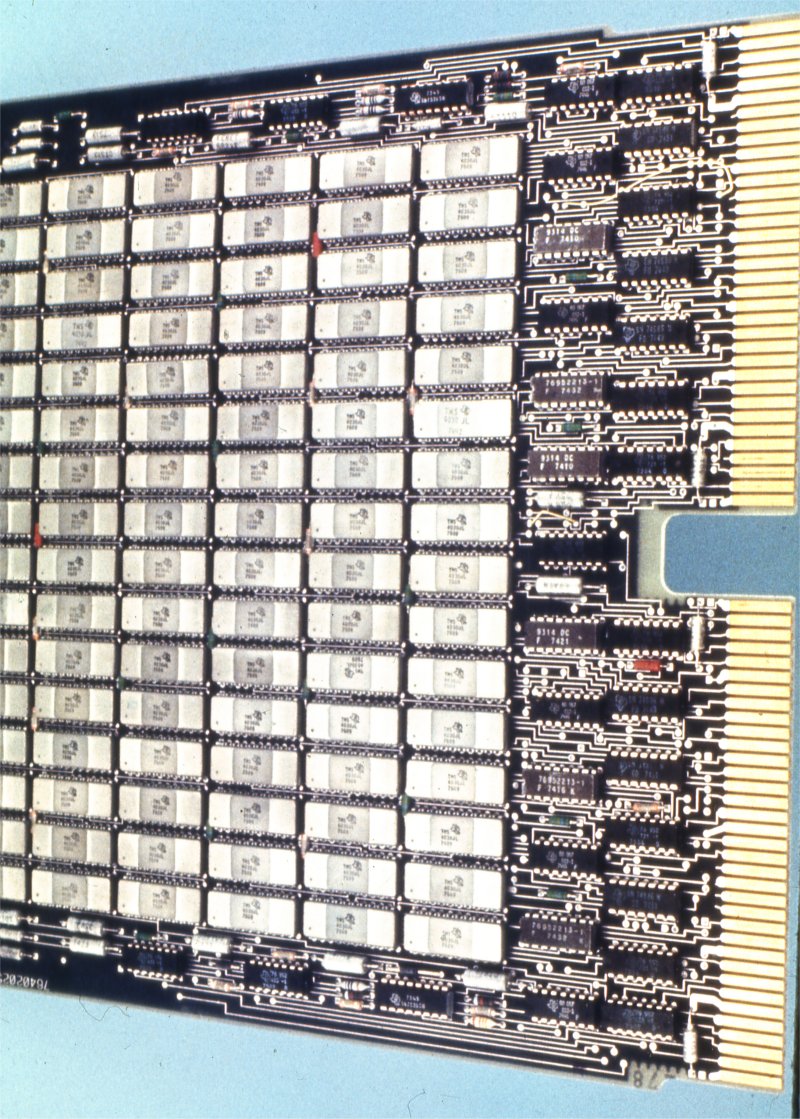

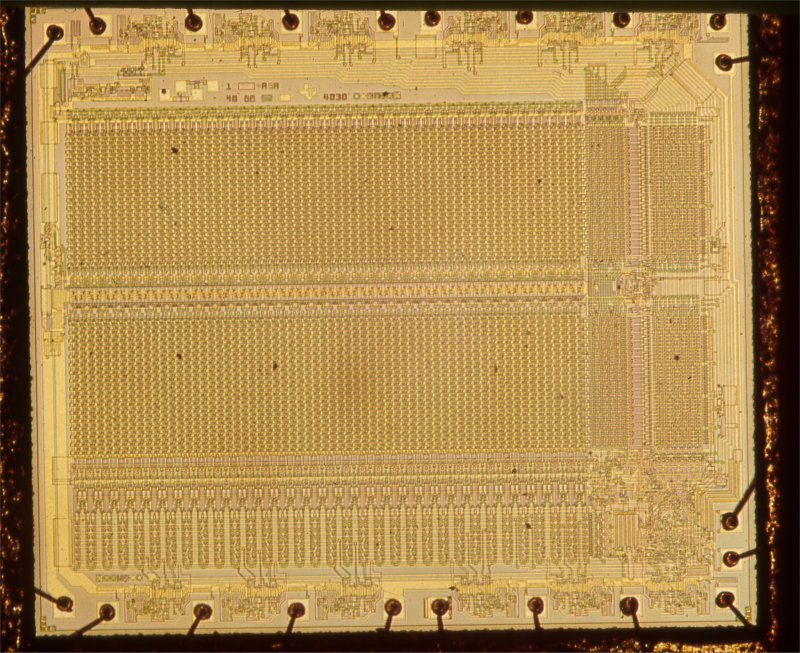

Plaques Level-64 -double

format-, à

gauche plaque mémoire, à gauche plaque logique |

Level-64 PWB boards, memory at left , logic at right |

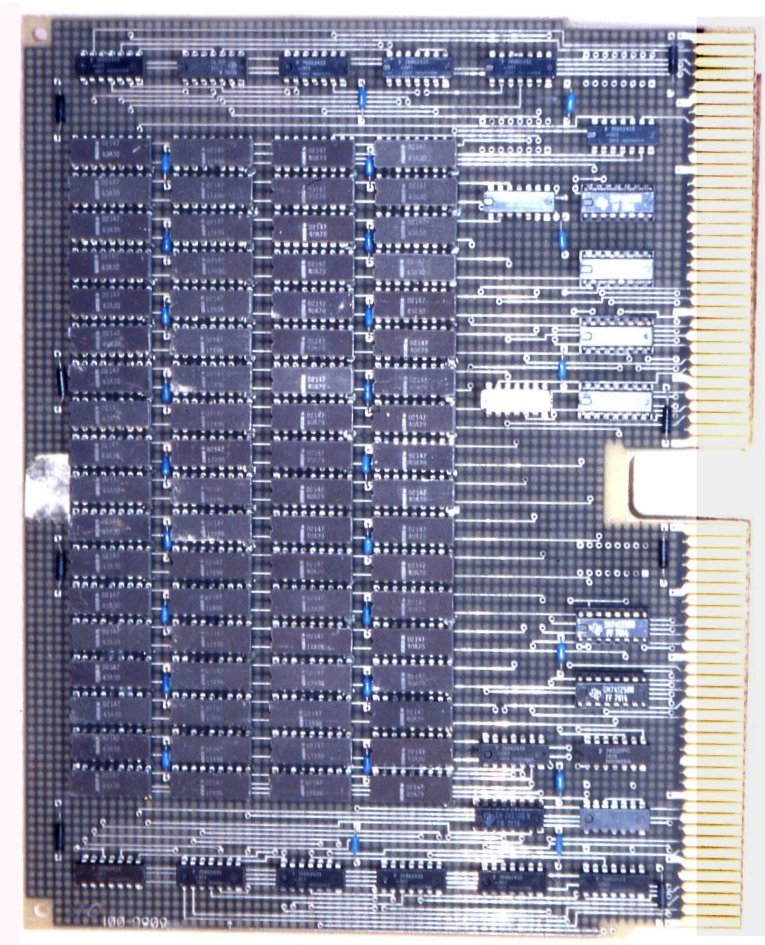

Mémoires DRAM

Le programme des Series-60 a été fondé sur l'utilisation des mémoires à semi-conducteurs DRAM dont on peut faire remarquer que Honeywell en avait été le promoteur auprès de Intel en 1969. La pré-série du 64 a été équipée de chips 1103 de 1024 bits, bien que le premier prototype ait reçu temporairement une mémoire à tores magnétiques.

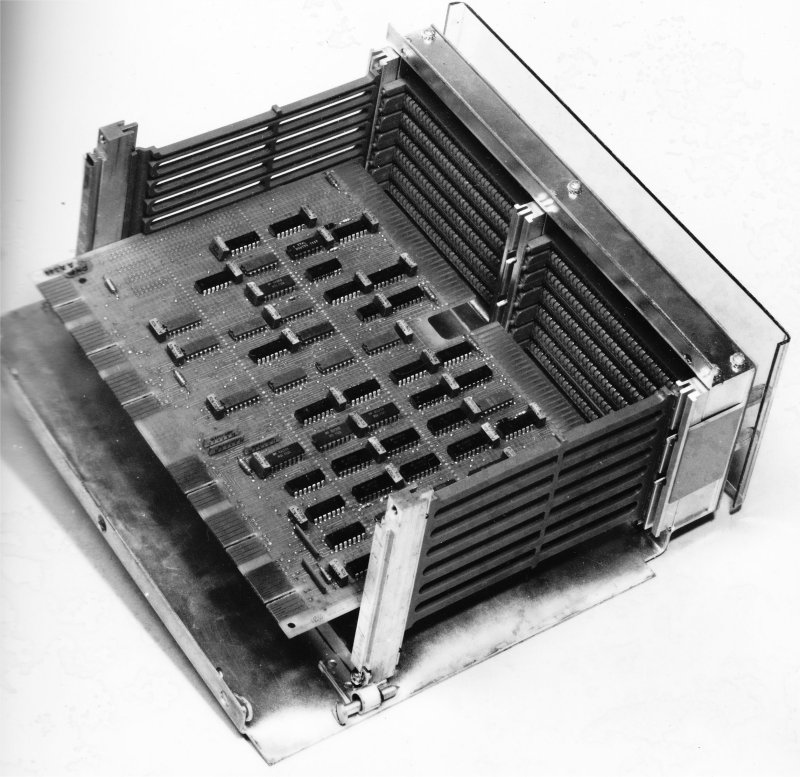

plaque mémoire avec chips 1024 x 1 bits comportant 8192 octets

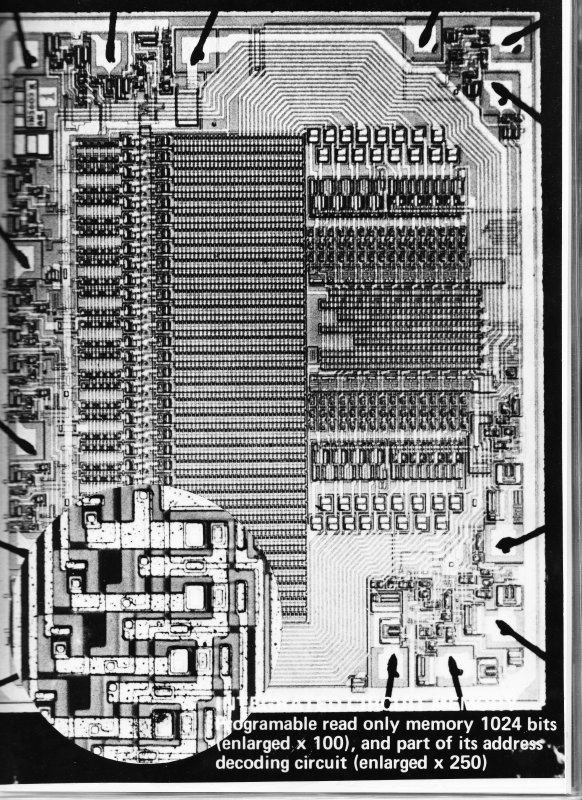

vue de la puce 1K

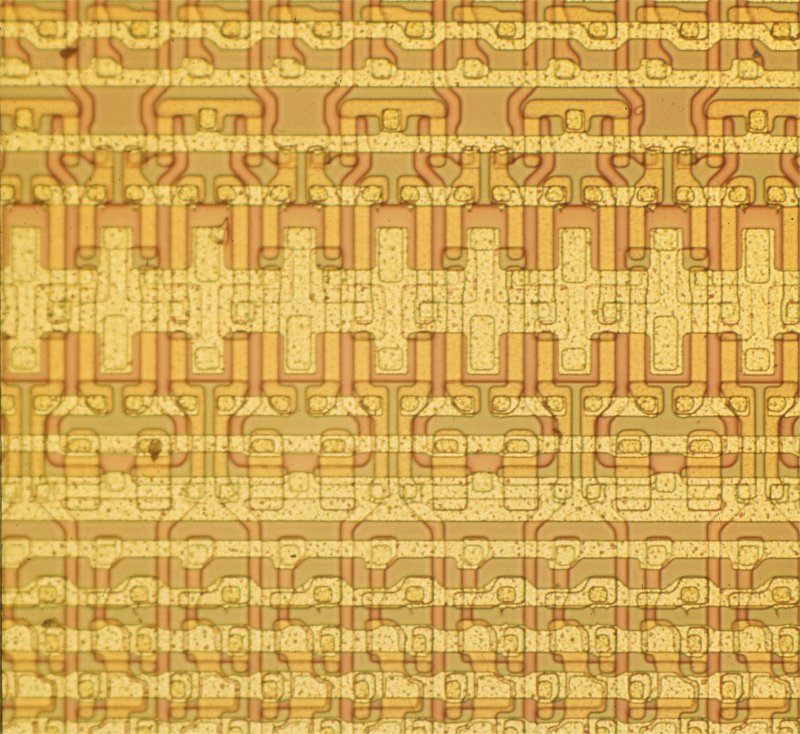

détail de la lithographie de la puce 1K

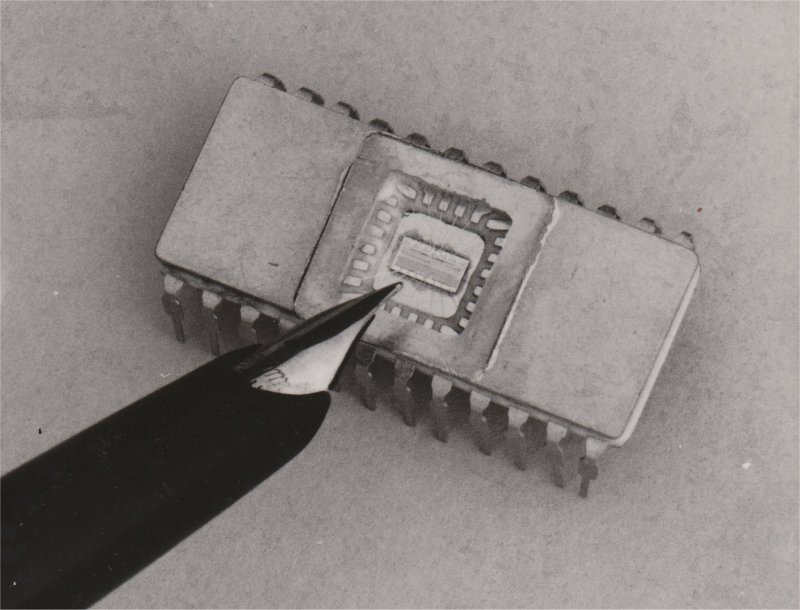

puce Kbit montée sur support Dual-in-line

La série des 64 a reçu dans ses fabrications à Angers des mémoire 4 Kbits, tandis que, devant un risque de pénurie qui s'est avéré non fondé, il a été fabriqué à Billerica des plaques mémoire avec des chips 2 K bits équipant des systèmes livrés aux Etats-Unis.

plaque mémoire contenant 16x 9 puces de 4K bits ( 64 K octets)

puce 4096 x 1 bits

Le 64-DPS lui sera livré avec des unités mémoires recevant des chips 4K bits ou 16 Kbits, prenant l'option conservée par la suite de désynchroniser la disponibilité des circuits mémoires et la livraison des systèmes.

Mémoire de contrôle PROM

La "mémoire morte" du 64 utilise une technologie à semi-conducteur de type PROM, achetée vierge et codée en usine.

plaque PROM

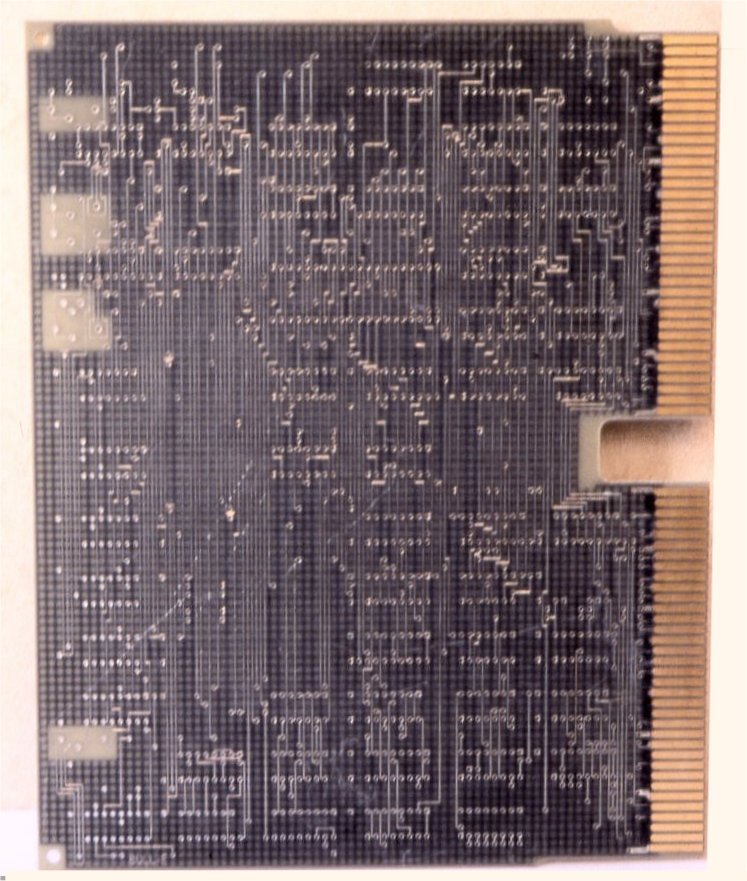

Circuits imprimés

Les différents types de circuits sont assemblés par l'usine de Angers sur des plaques (PWB Printed Wired Boards) de formats communs SP10 (simple et double hauteur) fabriquées par Honeywell-Bull. Deux modèles en existent selon la complexité de la logique : 4 couches ou 8 couches.

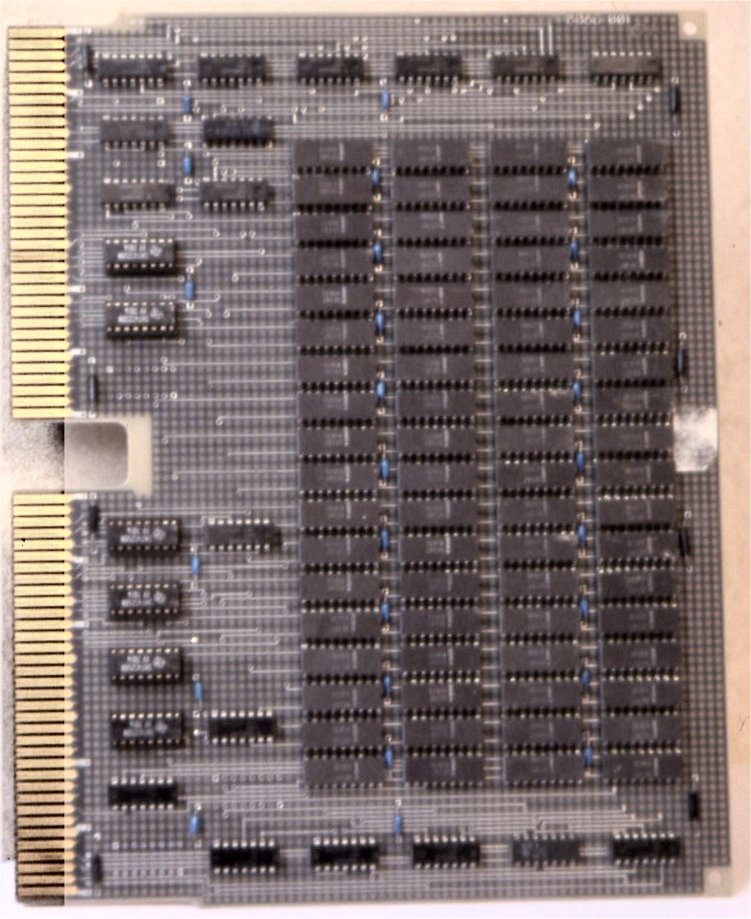

circuit imprimé nu avant montage des circuits intégrés

Si beaucoup de plaques n'ont qu'un seul connecteur de fond de panier, certaines doivent recevoir un second connecteur à l'avant

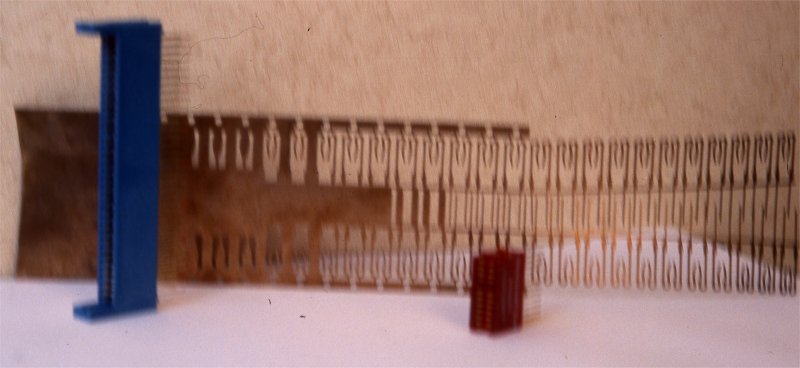

Connecteurs

Honeywell-Bull a conçu le connecteur CS-10 pour la technologie SP-10 du 64

Cette (mauvaise) photo montre:

En bleu : Connecteur SC1 à lyres 88 plots

En rouge : Connecteur 24 plots pour Internal External Cabling

en arrière plan: Bande d’usinage en continu des contacts/ Lyres en bronze

phosphoreux.

Nota : La réalisation de l’outil de

découpe a permis à un maître outilleur de Bull Anjou de se voir décerner en 1967

le titre de meilleur ouvrier de France.