1967-1975

| La gamme P fut la première série

de systèmes entrepris à titre du Plan Calcul par la CII Compagnie

Industrielle pour l'Informatique. Le premier système P1 fut commercialisée sous le nom de Iris 50. A noter que le système Iris 80 n'appartient pas à la même gamme et sera décrit par ailleurs. Son objectif était celui des applications de gestion, le même que ceux poursuivis par le rival franco-américain Bull-General Electric et évidemment celui de IBM. Un système P2 compatible avec l'Iris 50 fut introduit plus tard comme Iris60, deux modèles à fonctionnalités limitées Iris 45 et Iris 55 furent dérivés respectivement de l'Iris 50 et de l'Iris 60. Des versions militarisées Iris 35M et Iris 55M appartiennent également à la gamme Iris.

|

The computer Iris 50 was

produced by CII Compagnie Industrielle pour l'Informatique, as part of

Plan Calcul. It was the first system developed under that plan and the

only one that originated from scratch. Its

original code name was P1.

Its target was the business applications market, the main asset of the French rival Bull-General Electric and the stronghold of IBM. The P1 system was introduced by CII as Iris 50. A P2 system, compatible with P1, was introduced as Iris 60. Two reduced capability models Iris 45 and 55 were derived from respectively Iris 50 and 60 |

| Architecture (commune -sauf indiqué- à toutes les machines de la gamme) Le système traite des données organisées en octets de 8 bits. Le système adresse soit des chaines d'octets , soit des nombres décimaux de 4 bits (<31 chiffres), soit des nombres binaires de longueur fixe (31 bits + signe), soit des nombres binaires flottants simple ou double précision( 7 bits d'exposant -modulo 16- et 24 bits ou 56 bits de mantisse). Le système comporte 16 registres de 32 bits, les 8 derniers pouvant servir de registres de base.

Les instructions sont de longueur fixe (32-bits)

cadrées au mot. L'instruction comporte une adresse mémoire (indexée ou

non, indirecte ou non )et un registre général.

Lorsque l'adresse de l' opérandes est indexée, le registre de destination de l'opération est le registre 0. Les instructions décimales et virgule flottante sont optionnelles en matériel. En leur absence, elles sont interprétées par logiciel. La mémoire peut être (option) protégée par pages de 2 K octets. A chaque page est associée une "clé programme" de 4 bits qui est comparée au numéro de programme. Les disques sont adressés par secteurs de 256 octets. Modèles L'IRIS 50 (nom de code P1) fut le premier modèle introduit en face de l'IBM 350/50. Il a été annoncé en France en septembre 1968 et sa première livraison intervint le 13 février 1970. Un modèle "dégradé" l' Iris 45 fut annoncé le 25 mars 1971. L'Iris 60, positionné en face de l'IBM 370/145

et 155, avait été prévu initialement comme le modèle P2 de la gamme. Son

développement en fut repoussé et il fut finalement annoncé en septembre

1971. L'Iris 55 fut une version dégradée de l'Iris 60 annoncée le 15 janvier 1975. La gamme P comprend, en outre, l'Iris 55M

produite pour les sous-marins nucléaires lanceurs d'engins SNLE de la

Marine Française. Cette version militarisée et mise aux normes Marine

fut annoncée le 30 septembre 1970. Matériel Iris 50 Le système Iris 50 est composé de une unité processeur (UC), de une unité mémoire (UM) composée de 1 à 4 blocs mémoire indépendants et de une ou deux unités d'entrées-sorties (UEM unité d'échanges multiples). Chaque bloc de mémoire possède 2 ou 3 ports

indépendants de connexion avec le processeur ou l'UEM. L'UM comprend les

circuits de priorité d'accès communs à toutes les demandes d'accès. L'unité processeur (UC) est

responsable du décodage et de l'exécution des instructions, de

l'initialisation des transferts d'entrées-sorties et de la gestion des

interruptions.

Matériel Iris 60 Les instructions des programmes et du système d'exploitation de l'Iris 50 s'exécutent sans modification sur l'Iris 60. La taille de mémoire est étendue à 1024 K octets. La mémoire qui reste à tores magnétiques est adressée par mots de 32 bits. L'adressage se fait à travers une mémoire topographique permettant une relocation dynamique des programmes en mémoire inspirée de l'Iris 80. Cependant, cette possibilité ne sera pas utilisée par le logiciel.

Périphériques Logiciel Les systèmes d'exploitation de la série Iris 50/60 Siris2 et Siris 3 sont décrits dans une autre page Emulateur DPS-7 Il était envisagé, à CII, de réaliser un émulateur de Siris 3 sur certains modèles de la gamme X de Unidata. Mais ce plan n'a pas été réalisé. C'est sur le processeur CII-Honeywell-Bull DPS7-80 (nom de code P7G) que cet émulateur a finalement été réalisé sous la forme d'un mode Siris3 comprenant:

Le mode Siris 3 ne comprend pas de matériel

spécifique ni ne nécessitait la reconnexion et le support des

périphériques Iris.

|

Architecture

(common to all models of the product line) Data are 8-bits characters. Its instruction set used 32-bits fixed length instruction. The addressing was relative to mod-64 KB segments (opposed to smaller mod-4K in S/360). Memory addressing is limited to 256 KB on Iris 50 and 1024K on Iris 60.. Its discs were fixed length 256-bytes sectors

Models Iris 45 was an entry model, a downgraded Iris 50. It was announced March 25th 1971. Iris 50 was positioned faced to IBM 360/50. It was also produced under license in Romania as Felix C-256. Iris 50 was announced in France in September 1968 and the first shipment occurred February 13th, 1970. Iris 60 was positioned face to IBM

370/145 and 155. It was announced in September 1971. Iris 55 was a downgraded version of Iris 60, announced January 15th, 1973 A military ruggedized version Iris 55M was produced by CII for the French Navy, for the strategic submarines SNLE. It was introduced September 30th, 1970.

Iris 50 Hardware

Iris 60 Hardware

Software DPS-7 emulator The Siris 3 emulator on DPS7-80, included :

The system did not require new

hardware, nor the reconnection of Iris peripherals.

People The project responsibility was assigned to Gérard Cottet. The key designer of Iris 50 was B Fournier, the designer of Iris 60 was François Léger.

|

| BIBLIOGRAPHIE:

le système d'exploitation Siris 2 le système d'exploitation Siris 3

|

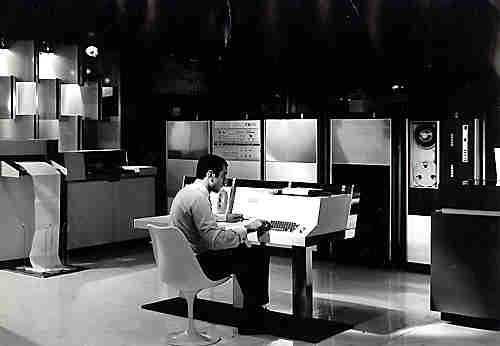

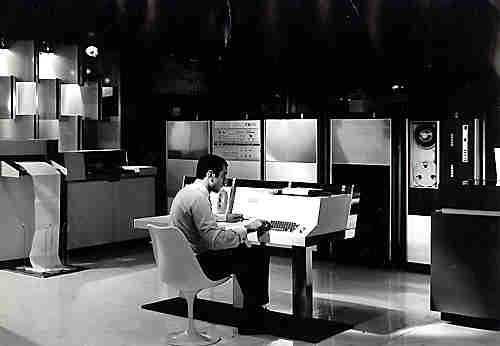

pupitre iris50

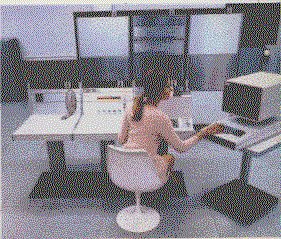

unité centrale iris 45

Revision : 23 février 2009 .