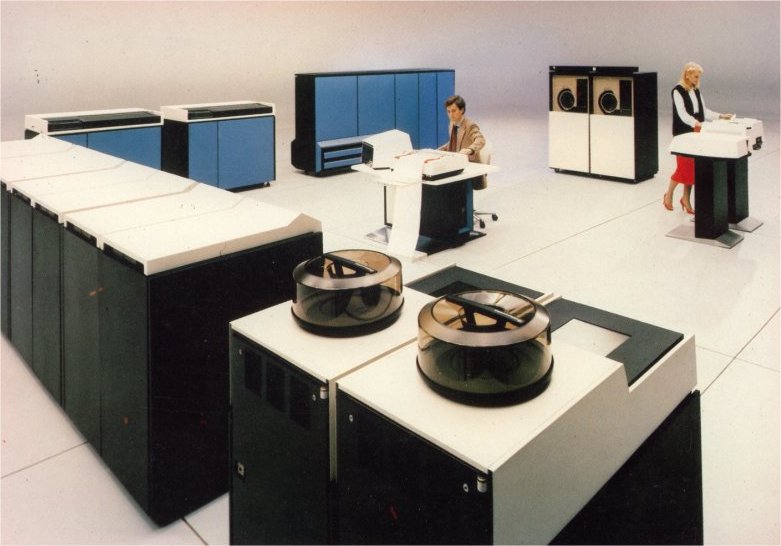

| Les systèmes dénommés DPS-7-x0

(c'est à dire 60, 70, 80 et 82) furent introduits en 1981 en haut de

gamme de la ligne GCOS7. Ces machines étaient de la même famille que les

systèmes Level 64 et Level 64 DPS, et la plupart des programmes, même

les programmes systèmes de GCOS64, fonctionnaient sous DPS-7. De plus, la

ligne DPS-7 comportait d'autres modèles DPS-7-x5 (nom de code Taurus)

d'architecture identique à celle du Level 64.

La rupture du nom de la ligne du 64 au DPS-7 et du système GCOS64 en GCOS7 fut de nature purement marketing. Cependant, les modèles DPS-7-X0 et leurs successeurs seront à même d'apporter des innovations sensibles qui ne seront pas visibles à l'annonce (Multiprocesseur, pagination...) Une autre caractéristique du DPS-7-x0 sera le

support d'émulateurs pour les logiciels (système et applications) du

parc CII Siris 3 et Siris 8. |

||

| Le système P7G a été conçu par une équipe dirigée par

Georges Lepicard entre 1976 et 1981. Le processeur l'a été dans

l'équipe ex-Honeywell-Bull de Jacques Bienvenu à Paris-Gambetta, les

entrées-sorties par une équipe ex-CII aux Clayes dirigée par Robert

Bavoux, le contrôleur mémoire et la technologie a été développée par

les équipes de Christian Joly à Saint-Ouen et à Angers, les modes (firmware

et software) l'ont été par des équipes ex-CII à Louveciennes et aux

Clayes. Le système a été intégré à Paris-Gambetta, les éléments des prototypes ont été fabriqués Angers ou la production en série a débuté en 1981/ |

PLAN |

OUTLINE |

|

|

architecture processeur |

system architecture processor architecture technology emulation modes |